# HMIC\_S IP User Guide

(UG042003, V1.14) 30.04.2024

Shenzhen Pango Microsystems Co., Ltd. All Rights Reserved. Any infringement will be subject to legal action.

# **Revisions History**

# **Document Revisions**

| Version | Date of Release | Revisions        | Applicable IP and<br>Corresponding Versions |

|---------|-----------------|------------------|---------------------------------------------|

| V1.14   | 30.04.2024      | Initial release. | V1.14                                       |

|         |                 |                  |                                             |

# **IP Revisions**

| IP Version | Date of Release | Revisions        |

|------------|-----------------|------------------|

| V1.14      | 30.04.2024      | Initial release. |

|            |                 |                  |

# **About this Manual**

### **Terms and Abbreviations**

| Terms and Abbreviations | Meaning                                      |  |

|-------------------------|----------------------------------------------|--|

| APB                     | Advanced Peripheral Bus                      |  |

| AXI                     | AdvancedeXtensible Interface                 |  |

| DDR                     | Double Data Rate                             |  |

| DFI                     | DDR PHY Interface                            |  |

| LP                      | Low Power                                    |  |

| MC                      | Memory Controller                            |  |

| MR                      | Mode Register                                |  |

| MRS                     | Mode Register Set                            |  |

| РНҮ                     | Physical                                     |  |

| RD                      | Read                                         |  |

| UI                      | User Interface                               |  |

| WR                      | Write                                        |  |

| DCD                     | DDR Command Decode                           |  |

| DCP                     | DDR3 Command Procedure                       |  |

| HMIC                    | High performance Memory Interface Controller |  |

| IPC                     | IP Compiler                                  |  |

| PDS                     | Pango Design Suite                           |  |

| PCE                     | Physical Constraint Editor                   |  |

| UCE                     | User Constraint Editor                       |  |

|                         |                                              |  |

# **Related Documentation**

The following documentation is related to this manual:

- 1. Pango\_Design\_Suite\_Quick\_Start\_Tutorial

- 2. Pango\_Design\_Suite\_User\_Guide

- 3. IP\_Compiler\_User\_Guide

- 4. Simulation\_User\_Guide

- 5. User\_Constraint\_Editor\_User\_Guide

- 6. Physical\_Constraint\_Editor\_User\_Guide

- 7. Route\_Constraint\_Editor\_User\_Guide

8. JESD79-3D, DDR3 SDRAM Standard

9. JESD79-2F, DDR2 SDRAM SPECIFICATION

10. JESD209B, Low Power Double Data Rate (LPDDR) SDRAM Standard

11. DDR PHY Inteface, DFI 3.1 Specification

12. UG050012\_Titan2 Single Board Hardware Design Guide

13. UG040012\_Logos2 Single Board Hardware Design User Guide

# **Table of Contents**

| Revisions History<br>About this Manual        |        |

|-----------------------------------------------|--------|

|                                               |        |

| Table of Contents                             |        |

| Tables                                        |        |

| Figures                                       |        |

| Chapter 1 Preface                             |        |

| 1.1 Introduction of the Manual                |        |

| 1.2 Writing Standards of the Manual           |        |

| Chapter 2 IP User Guide                       |        |

| 2.1 IP Introduction                           |        |

| 2.1.1 Key Features                            |        |

| 2.1.2 Applicable Devices and Packages         |        |

| 2.2 IP Block Diagram                          |        |

| 2.2.1 Controller + PHY                        |        |

| 2.2.2 PHY Only                                |        |

| 2.3 IP Generation Process                     |        |

| 2.3.1 Module Instantiation                    |        |

| 2.3.2 Constraint Configuration                |        |

| 2.3.3 Simulation Runs                         |        |

| 2.3.4 Synthesis and Placement/Routing         |        |

| 2.3.5 Resources Utilization                   |        |

| 2.4 Example Design                            |        |

| 2.4.1 Design Block Diagram                    |        |

| 2.4.2 Test Method                             |        |

| 2.5 Descriptions of IP Interfaces             |        |

| 2.5.1 Controller Interface Description        |        |

| 2.5.2 Controller Interface Timing Description |        |

| 2.5.3 PHY Interface Description               |        |

| 2.5.4 PHY Interface Timing Description        |        |

| 2.5.5 Debug Data Description                  |        |

| 2.6 Description of the IP Register            |        |

| 2.6.1 Register Description                    |        |

| 2.6.2 Register Access                         |        |

| 2.7 Typical Applications                      |        |

| 2.8 Descriptions and Considerations           |        |

| 2.8.1 AXI4 Interface Burst Calculation        |        |

| 2.8.2 Column Address Rounding Examples        |        |

| (UG042003, V1.14)                             | 4 / 67 |

| 2.8.3 Clock Constraints                   |  |

|-------------------------------------------|--|

| 2.8.4 IO Constraints                      |  |

| 2.8.5 Route Constraints                   |  |

| 2.8.6 SCBV Setting                        |  |

| 2.9 IP Debugging Method                   |  |

| 2.9.1 Key Indicator Signal                |  |

| 2.9.2 Internal status and control signals |  |

| Disclaimer                                |  |

| Table 1-1 Description of Writing Standards                                              | 9      |

|-----------------------------------------------------------------------------------------|--------|

| Table 2-1 HMIC_S IP Applicable Devices and Packages                                     | 11     |

| Table 2-2 Descriptions of Configuration Parameters on the Basic Options Page            |        |

| Table 2-3 Descriptions of Configuration Parameters on the Memory Options Page           |        |

| Table 2-4 Description of Configuration Parameters on Pin/Bank Options Page              |        |

| Table 2-5 Output Files after IP Generation                                              |        |

| Table 2-6 Typical Resource Utilization Values for HMIC_S IP Based on Applicable Devices |        |

| Table 2-7 Global Interface                                                              |        |

| Table 2-8 Write Address Channel                                                         |        |

| Table 2-9 Read Address Channel                                                          |        |

| Table 2-10 Write Data Channel                                                           |        |

| Table 2-11 Read Data Channel                                                            |        |

| Table 2-12 Write Address Channel                                                        |        |

| Table 2-13 Read Address Channel                                                         |        |

| Table 2-14 Write Data Channel                                                           |        |

| Table 2-15 Read Data Channel                                                            |        |

| Table 2-16 Config Interface                                                             |        |

| Table 2-17 DFI Interface                                                                |        |

| Table 2-18 Differences between Simplified AXI4 and Standard AXI4                        |        |

| Table 2-19 Detailed Differences between Simplified AXI4 and Standard AXI4               |        |

| Table 2-20 Clock and Reset Interface                                                    |        |

| Table 2-21 DFI Interface                                                                |        |

| Table 2-22 Memory Interface                                                             |        |

| Table 2-23 Debug Interface                                                              |        |

| Table 2-24 Differences between the DFI Interface of this Design and Standard DFI        | 50     |

| Table 2-25 Detailed Comparison of Differences between DFI Interface and Standard DFI    | 51     |

| Table 2-26 Definitions of debug_data Fields                                             | 55     |

| Table 2-27 Definitions of debug_calib_ctrl Fields                                       | 55     |

| Table 2-28 Definitions of dbg_slice_state Fields                                        | 56     |

| Table 2-29 Definitions of dbg_slice_state Fields                                        | 57     |

| Table 2-30 Definitions of MODE_REG_0_ADDR Bits                                          |        |

| Table 2-31 Definitions of MODE_REG_1_ADDR Bits                                          |        |

| Table 2-32 Definitions of MODE_REG_2_ADDR Bits                                          | 59     |

| Table 2-33 Definitions of MODE_REG_3_ADDR Bits                                          | 59     |

| Table 2-34 Definitions of CTRL_MODE_DATA Bits                                           | 59     |

| Table 2-35 Definitions of STATUS_REG_DATA Bits                                          | 60     |

| Table 2-36 SCBV Setting Rules                                                           | 64     |

| (UG042003, V1.14)                                                                       | 6 / 67 |

| Table 2-37 Key Indicator Signal                            |  |

|------------------------------------------------------------|--|

| Table 2-38 DDRPHY Example Design Serial Port Configuration |  |

Tables

| Figure 2-1 HMIC_S IP System Block Diagram                       |    |

|-----------------------------------------------------------------|----|

| Figure 2-2 HMIC_S IP Path Selection Interface                   | 14 |

| Figure 2-3 Project Instantiation Interface                      | 14 |

| Figure 2-4 HMIC_S IP Interface Block Diagram                    |    |

| Figure 2-5 HMIC_S IP Parameter Configuration Interface          |    |

| Figure 2-6 Basic Options Page                                   |    |

| Figure 2-7 Memory Options Page                                  |    |

| Figure 2-8 Pin/Bank Options Page                                |    |

| Figure 2-9 Summary Page                                         |    |

| Figure 2-10 HMIC_S IP Generation Report Interface               |    |

| Figure 2-11 Open ModelSim Instruction                           |    |

| Figure 2-12 ModelSim Simulation Execution Script                |    |

| Figure 2-13 VCS Simulation Script Execution                     |    |

| Figure 2-14 Example Design System Block Diagram                 |    |

| Figure 2-15 Example Design Test Flowchart                       |    |

| Figure 2-16 Memory Address 1 Mapped From AXI4 Interface Address |    |

| Figure 2-17 Memory Address 2 Mapped From AXI4 Interface Address |    |

| Figure 2-18 Typical Timing for Write Address                    |    |

| Figure 2-19 Typical Timing for Read Address                     |    |

| Figure 2-20 Typical Timing for Write Data                       |    |

| Figure 2-21 Typical Timing for Read Data                        |    |

| Figure 2-22 Typical Timing for Write Address                    |    |

| Figure 2-23 Typical Timing for Read Address                     |    |

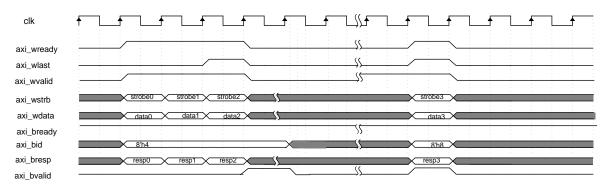

| Figure 2-24 Typical Timing for Write Data                       |    |

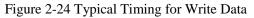

| Figure 2-25 Typical Timing for Read Data                        |    |

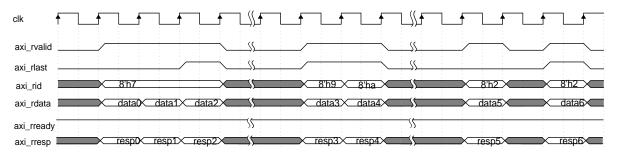

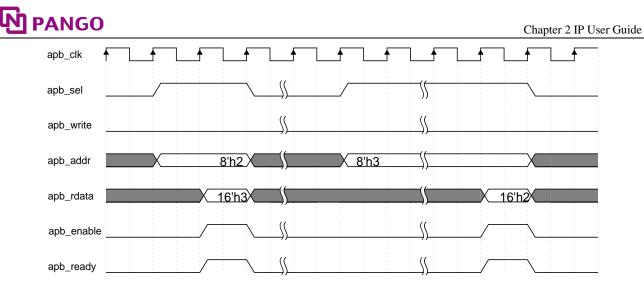

| Figure 2-26 Typical Write Timing of the APB Interface           |    |

| Figure 2-27 Typical Read Timing of the APB Interface            |    |

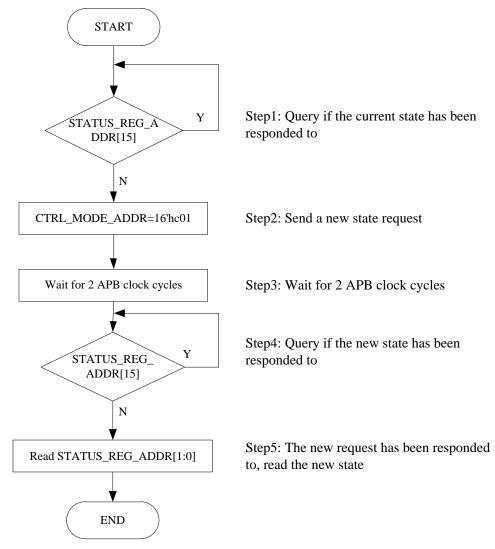

| Figure 2-28 DDR3 Status Request Switching Flowchart             |    |

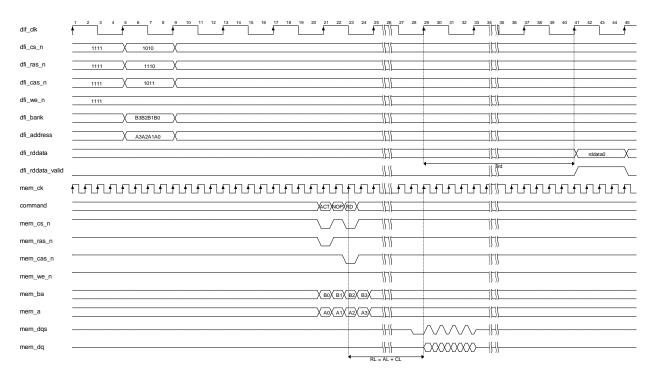

| Figure 2-29 DFI Interface Write Operation Timing                |    |

| Figure 2-30 DFI Interface Read Operation Timing                 |    |

| Figure 2-31 Multi-bank-x64 Structure Diagram                    | 61 |

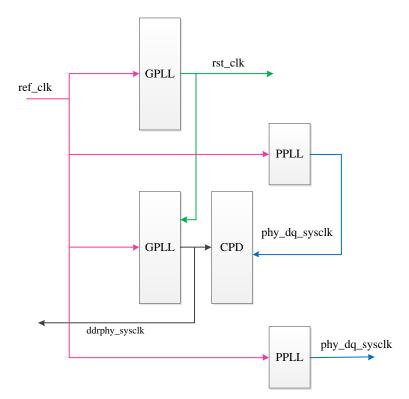

| Figure 2-32 IP Internal Clock Structure                         |    |

| Figure 2-33 SCBV Setting Interface                              |    |

|                                                                 |    |

# **Chapter 1 Preface**

This chapter describes the scope, structure, and writing standards of this manual to help users quickly find the information they need.

### **1.1 Introduction of the Manual**

This manual serves as the user guide for the DDR3 IP—HMIC\_S (High-performance Memory Interface Controller Soft core) IP launched by Pango Microsystems. The content of this manual primarily includes the IP user guide and related information. This manual helps users quickly understand the HMIC\_S IP features and usage.

### **1.2 Writing Standards of the Manual**

| Text                                                                                                                                         | Rules                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Attention If users ignore the attention contents, they may suffer adverse consequences or fai operate successfully due to incorrect actions. |                                                  |

| Description                                                                                                                                  | Instructions and tips provided for users.        |

| Recommendation                                                                                                                               | Recommended settings and instructions for users. |

# **Chapter 2 IP User Guide**

This chapter provides a guide on the use of HMIC\_S IP, including an introduction to IP, block diagram, IP generation process, Example Design, IP interface description, IP register description, typical applications, instructions and considerations, and IP debugging methods. More details on the design process can be found in the following PDS help documentation.

- "Pango\_Design\_Suite\_Quick\_Start\_Tutorial"

- "Pango\_Design\_Suite\_User\_Guide"

- "IP\_Compiler\_User\_Guide"

- "Simulation\_User\_Guide"

# **2.1 IP Introduction**

HMIC\_S IP is a DDR3 IP launched by Pango Microsystems. It is compatible with LPDDR and DDR2. Users can configure and generate the IP modules using the IPC (IP Compiler) in the PDS (Pango Design Suite).

# 2.1.1 Key Features

The main features of the HMIC\_S IP product are as follows.

- Supports DDR3, DDR2 and LPDDR;

- Supports a maximum data width of 72 bits;

- ➢ User interface: reduced AXI4 bus interface and APB bus interface;

- Supports configurable low-power modes: Self-Refresh and Power Down;

- Supports up to 1066Mbps data rate for DDR3;

- Supports up to 800Mbps data rate for DDR2;

- Supports up to 400Mbps data rate for LPDDR;

- Burst Length 8 and single Rank;

- Available as a separate PHY use.

2.1.2 Applicable Devices and Packages

| Applicable Devices | Supported Packages     |

|--------------------|------------------------|

| PG2L25H            | MBG325                 |

| PG2L50H            | MBG324/FBG484          |

| PG2L100H           | FBG676/FBG484/MBG324   |

| PG2L100HX          | FBG676/FBG484/MBG324   |

| PG2L200H           | FBB484/FBB676/FFBG1156 |

| PG2T390H           | FFBG900/FFBG676        |

| PG2K400            | FFBG900/FFBG676        |

| PG2T70H            | FBB484/FBB676          |

| PG2T390HX          | FFBG900/FFBG676        |

| PG2T160H           | FBB484/FFBG676         |

| Table 2-1 HMJ | C_S IP App | olicable Devices | and Packages |

|---------------|------------|------------------|--------------|

|---------------|------------|------------------|--------------|

# 2.2 IP Block Diagram

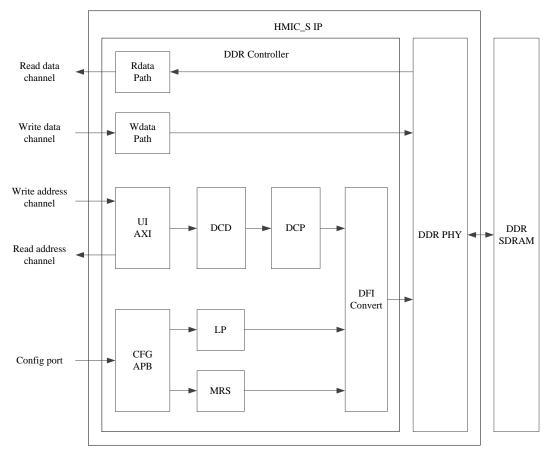

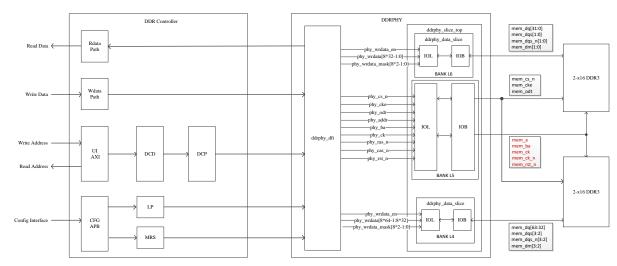

The system block diagram of HMIC\_S IP is shown in Figure 2-1. HMIC\_S IP supports two operating modes: Controller + PHY, or PHY Only.

# 2.2.1 Controller + PHY

In this mode, the IP includes DDR Controller and DDR PHY functions. Users read and write data through the AXI4 interface, and use the APB interface for low power mode and MRS control.

# ➢ AXI4 Interface

This interface comprises four parts: write address channel, read address channel, write data channel, and read data channel.

Users initiate read and write operations through the write and read address channels; the commands are parsed into internal controller commands in the UI AXI module; then decomposed into corresponding DDR commands in the DCD (DDR Command Decode) module; timing control based on DDR is implemented in the DCP (DDR3 Command Procedure) module; converted into the DFI interface in the DFI Convert module, transferred to PHY, and finally to the DDR Memory interface.

Write data is passed through the write data channel interface, directly through the Wdata Path module to the DDR PHY, and ultimately transferred to the DDR Memory interface.

Read data from DDR Memory, after being sampled and parsed by the DDR PHY, is synchronized through the Rdata Path module and returned to the user through the read data channel interface.

# Config port

This interface is an APB configuration interface through which users can read the status of DDR SDRAM and implement low power mode and MRS control.

# 2.2.2 PHY Only

In this mode, users need to design the Controller by their own, and interconnect the PHY with DFI interface to operate the DDR SDRAM.

# 2.3 IP Generation Process

#### 2.3.1 Module Instantiation

Customized configurations of HMIC\_S IP can be completed through the IPC tool, instantiating the

required IP modules. For detailed instructions on using the IPC tool, please refer to "IP\_Compiler\_User\_Guide".

The main steps for instantiating the HMIC\_S IP module are described below.

# 2.3.1.1 Selecting IP

Open IPC and click File > Update in the main window to open the Update IP dialog box, where you add the corresponding version of the IP model.

After selecting the FPGAs device type, the Catalog interface displays the loaded IP models. Select the corresponding version of DDR3 Interface under the "System/DDR/Soft" directory. The IP selection path is shown in Figure 2-2. Then set the Pathname and Instance Name on the right side of the page. The project instantiation interface is shown in Figure 2-3.

#### Attention:

PG2L25H, PG2L50H: The software version must be 2022.1 or above;

PG2L100H, PG2T390H: The software version must be 2021.1-SP7.6 or above;

PG2L200H: The software version must be 2022.2-SP1.2 or above;

PG2L100HX: The software version must be 2023.1 or above;

PG2K400: The software version must be 2023.2 or above;

PG2T70H: The software version must be 2023.2 or above;

PG2T390HX: The software version must be 2022.2-SP6.4 or above;

PG2T160H: For the software version, please consult FAE.

| Catalog    | Project |   |

|------------|---------|---|

| IP (16/71) |         | Δ |

| 🕀 🧰 Module |         |   |

| 🖻 🚞 System |         |   |

| 🗄 💼 ddr    |         |   |

| 🗄 🧰 So     | ft      |   |

|            |         |   |

Figure 2-2 HMIC\_S IP Path Selection Interface

| Pathname      | D:\TEST\ipcore\test\test.idf |           | Browse | Proj Path |  |

|---------------|------------------------------|-----------|--------|-----------|--|

| Instance Name | test                         | Customize |        |           |  |

Figure 2-3 Project Instantiation Interface

# 2.3.1.2 IP Parameter Configuration

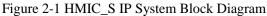

After selecting the IP, click <Customize> to enter the HMIC\_S IP parameter configuration interface. The left Symbol is the interface block diagram, as shown in Figure 2-4; the Parameter Configuration window is shown on the right side, as shown in Figure 2-5.

| Symbol                             | -                                                               |

|------------------------------------|-----------------------------------------------------------------|

| ref_clk                            |                                                                 |

| resetn                             |                                                                 |

| axi awaddr[26:0]                   |                                                                 |

| axi awuser ap-                     |                                                                 |

|                                    |                                                                 |

| axi_awuser_id[3:0]                 |                                                                 |

| axi_awlen[3:0] →                   |                                                                 |

| axi_awvalid —•                     | →axi_wusero_id[3:0]                                             |

| axi_wdata[127:0]                   | →axi_wusero_last                                                |

| axi_wstrb[15:0]                    | →axi_arready                                                    |

| axi_araddr[26:0]                   | axi_rdata[127:0]                                                |

| axi_aruser_ap                      | →axi_rvalid                                                     |

| axi_aruser_id[3:0]                 | axi_rid[3:0]                                                    |

| axi arlen[3:0]                     |                                                                 |

| axi arvalid -                      | →apb_ready                                                      |

| apb clk →                          | →mem_a[13:0]                                                    |

| apb_rst_n →                        | →mem_ba[2:0]                                                    |

|                                    | >mem_ck                                                         |

| apb_sel                            | →mem_ck_n                                                       |

| apb_enable →                       | >mem_cke                                                        |

| apb_addr[7:0]                      | →mem_dm[1:0]                                                    |

| apb_write                          | >mem_odt                                                        |

| apb_wdata[15:0]                    | >mem_cs_n                                                       |

| apb_rdata[15:0] →                  | →mem_ras_n                                                      |

| dbg_gate_start                     | →mem_cas_n                                                      |

| dbg_cpd_start                      | →mem_we_n                                                       |

| dbg_ddrphy_rst_n                   | ->mem_reset_n                                                   |

| dbg gpll scan rst -                | ← mem_dq[15:0]                                                  |

| dbg dll update en —                | ← mem_dqs[1:0]                                                  |

| samp position dyn adj              | ⊷mem_dqs_n[1:0]                                                 |

|                                    | debug_calib_ctr1[29:0]                                          |

| init_samp_position_even[15:0] -    | <pre>dbg_slice_status[33:0]</pre>                               |

| init_samp_position_odd[15:0]       | <pre>dbg_slice_state[43:0]</pre>                                |

| wrcal_position_dyn_adj             | debug_data[131:0]                                               |

| init_wrcal_position[15:0]          | <pre>dbg_dll_upd_state[1:0]</pre>                               |

| force_read_clk_ctrl                | <pre>debug_gpl1_dps_phase[8:0]</pre>                            |

| <pre>init_read_clk_ctrl[5:0]</pre> | <pre>dbg_rst_dps_state[3:0]</pre>                               |

| init_slip_step[7:0]                | <pre>dbg_tran_err_rst_cnt[5:0]</pre>                            |

| debug_cpd_offset_adj               | <pre>&gt;dbg_ddrphy_init_fail &gt;dobug_drp_ort_dim0[0:0]</pre> |

| debug cpd offset dir               | <pre>debug_dps_cnt_dir0[9:0]</pre>                              |

| debug cpd offset[9:0]              | → debug_dps_cnt_dirl[9:0]                                       |

|                                    | <pre>debug_rst_state[3:0]</pre>                                 |

|                                    | debug_cpd_state[3:0]                                            |

| Step 1: Basic Options Step 2 | 2: Memory Options  | Step 3: H  | in/Bank Options  | Step 4: Summary |  |  |  |  |

|------------------------------|--------------------|------------|------------------|-----------------|--|--|--|--|

| Type Options                 |                    |            |                  |                 |  |  |  |  |

| Please select the memory i   | nterface type from | n the Memo | ry Type selectio | on.             |  |  |  |  |

| Memory Type:                 | DDR3               | ~          |                  |                 |  |  |  |  |

| Mode Options                 | Mode Options       |            |                  |                 |  |  |  |  |

| Please select the operatin   | g mode for memory  | Interface  |                  |                 |  |  |  |  |

| Operating Mode:              | Controller + PHY   | ×          |                  |                 |  |  |  |  |

| Memory Address Mapping Sel   | ection             |            |                  |                 |  |  |  |  |

| AxA0                         |                    |            |                  |                 |  |  |  |  |

| ROW + BANK + COLUMN          |                    |            |                  |                 |  |  |  |  |

| O BANK + ROW + COLUMN        |                    |            |                  |                 |  |  |  |  |

| Width Options                |                    |            |                  |                 |  |  |  |  |

| Please select the data wid   | th which memory in | nterface c | an access at a t | time.           |  |  |  |  |

| Total Data Width:            | 16                 | ~          |                  |                 |  |  |  |  |

| Clock settings               |                    |            |                  |                 |  |  |  |  |

| Input Clock Frequency:       | 50.000             | \$         | MHz(range:20-80) | OMHz)           |  |  |  |  |

| Desired Data Rate:           | 800.000            | \$         | Mbps(range:600-  | 1066.666Mbps)   |  |  |  |  |

| Actual Data Rate:            | 800.0              |            | Mops             |                 |  |  |  |  |

| Write and Read Latency       |                    |            |                  |                 |  |  |  |  |

| CAS Write Latency(CWL):      | 5                  | ~          | tCK(range: 5)    |                 |  |  |  |  |

| CAS Latency(CL):             | 6                  | ~          | tCK(range: 5-6)  | )               |  |  |  |  |

| Additive Latency(AL):        | CL-2               | ~          | tCK              |                 |  |  |  |  |

Figure 2-5 HMIC\_S IP Parameter Configuration Interface

#### Attention:

Please be sure to configure the IP parameters in the order of the pages, following Step  $1 \rightarrow$  Step  $2 \rightarrow$  Step  $3 \rightarrow$  Step 4.

Parameter configuration includes four pages, namely Step1: Basic Options, Step 2: Memory Options, Step 3: Pin/Bank Options, Step 4: Summary. The configuration steps for HMIC\_S IP are described as follows.

# 2.3.1.2.1 Step 1: Basic Options

Basic Options is the fundamental configuration page for the IP, as shown in Figure 2-6. Please refer to Table 2-2 for detailed parameters.

| Step 1: Basic Options Step 2: Memory Options | Step 3: Pin/Bank Options Step 4: Summary |                                |

|----------------------------------------------|------------------------------------------|--------------------------------|

| Type Options                                 |                                          |                                |

| Please select the memory interface type fro  | n the Memory Type selection.             |                                |

| Memory Type:                                 | DDR3 V                                   |                                |

| Mode Options                                 |                                          |                                |

| Please select the operating mode for memory  | Interface.                               |                                |

| Operating Mode:                              | Controller + PHY                         |                                |

| AXI Interface Mode Options                   |                                          |                                |

| AxA0                                         |                                          |                                |

| Standard AXI Interface                       |                                          |                                |

| Simplified AXI Interface                     |                                          |                                |

| Memory Address Mapping Selection             |                                          |                                |

| AxA0                                         |                                          |                                |

| ROW + BANK + COLUMN                          |                                          |                                |

| BANK + ROW + COLUMN                          |                                          |                                |

| Width Options                                |                                          |                                |

| Please select the data width which memory i  | nterface can access at a time.           |                                |

| Total Data Width:                            | 16                                       |                                |

| Clock settings                               |                                          |                                |

| Input Clock Frequency:                       | 50.000                                   | MHz (range: 20-300MHz)         |

| Desired Data Rate:                           | 800.000                                  | Mbps (range: 600-1666.6688bps) |

| Actual Data Rate:                            | 800.0                                    | Kopa                           |

| -Write and Read Latency                      |                                          |                                |

| CAS Write Latency(CWL):                      | 5                                        | CK(range: 5)                   |

| CAS Latency(CL):                             | 6                                        | vCK(range: 5-6)                |

| Additive Latency(AL):                        | CL-2 V                                   | UTK CTK                        |

Figure 2-6 Basic Options Page

| Option Domain                                       | Option<br>Name/Parameter<br>Name | Parameter Description                                                                                                                                                                                                                                                                                                                  | Default<br>Value |

|-----------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Type Options                                        | Memory Type                      | The type of SDRAM used, the currently optional type is:<br>DDR3.                                                                                                                                                                                                                                                                       | DDR3             |

| Mode Options                                        | Operating Mode                   | <ul> <li>HMIC_S operating mode selection. The available operating modes are:</li> <li>1) Controller +PHY</li> <li>2) PHY Only;</li> <li>If Controller +PHY is selected, the generated IP code includes both the Controller and PHY;</li> <li>If PHY Only is selected, the generated IP code will only include the PHY part.</li> </ul> | PHY Only         |

| AXI Interface                                       | Standard AXI<br>Interface        | Select the Controller AXI interface as Standard AXI4 mode;                                                                                                                                                                                                                                                                             | Selected         |

| Mode Options <sup>1</sup>                           | Simplified AXI interface         | Select the Controller AXI interface as Simplified AXI4 mode;                                                                                                                                                                                                                                                                           | Cleared          |

| Memory Address<br>Mapping<br>Selection <sup>2</sup> | ROW + BANK +<br>COLUMN           | The read/write address mapping method for the<br>Controller AXI interface is selected as:<br>"ROW + BANK + COLUMN", please refer to<br>Figure 2-16.                                                                                                                                                                                    | Selected         |

|                                                     | BANK + ROW +<br>COLUMN           | The read/write address mapping method for the<br>Controller AXI interface is selected as:<br>"BANK + ROW + COLUMN", please refer to<br>Figure 2-17.                                                                                                                                                                                    | Cleared          |

| Width Options                                       | Total Data Width <sup>3</sup>    | The total DQ width of the off-chip SDRAM<br>connected to HMIC_S. Supported total widths<br>include:<br>72<br>64<br>56<br>48<br>40<br>32<br>24<br>16<br>8                                                                                                                                                                               | 16               |

Table 2-2 Descriptions of Configuration Parameters on the Basic Options Page

1 This option is only displayed when the Operating Mode is "Controller + PHY".

<sup>2~</sup> This option is only displayed when the Operating Mode is "Controller + PHY".

<sup>3</sup> The PG2L100H in FBG484 and MBG324 packages, as well as all PG2L25H and PG2L50H packages, only support a width of up to 32.

| Option Domain             | Option<br>Name/Parameter<br>Name                                                                 | Parameter Description                                                                                                                                                                  | Default<br>Value |

|---------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|                           | Input Clock<br>Frequency                                                                         | The input clock of HMIC_S, in MHz.                                                                                                                                                     | 50               |

| Clock Settings            | Desired Data Rate <sup>4</sup>                                                                   | Desired data rate.<br>The maximum speed supported by DDR3 is<br>1066Mbps.<br>The maximum speed supported by DDR2 is<br>800Mbps.<br>The maximum speed supported by LPDDR is<br>400Mbps. | 800Mbps          |

|                           | Actual Data Rate The actual data rate, which should be as close to the desired rate as possible. |                                                                                                                                                                                        | -                |

|                           | CAS Write<br>Latency(CWL)                                                                        | CAS Write Latency configuration, in tCK. (Only DDR3 is displayed)                                                                                                                      | 5                |

| Write and Read<br>Latency | CAS Latency(CL) CAS Latency configuration, in tCK. (Only DDR3 is displayed)                      |                                                                                                                                                                                        | 6                |

|                           | Additive<br>Latency(AL)                                                                          | Additive Latency configuration, in tCK. (Only DDR3 is displayed)                                                                                                                       | CL-2             |

Note: "-" indicates that there is no default value for this parameter in the IP configuration interface.

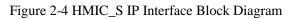

# 2.3.1.2.2 Step 2: Memory Options

Memory Options is the configuration page for Memory parameters, as shown in Figure 2-7. For detailed parameters, please refer to Table 2-3.

Figure 2-7 Memory Options Page

<sup>4</sup> The default value for this parameter is related to the "Memory Type," DDR3: 800Mbps; DDR2: 600Mbps; LPDDR: 200Mbps.

| Option<br>Domain                      | Option<br>Name/Parameter<br>Name   | Parameter Description                                                                                                                                                                                                                                          | Default<br>Value                                                                                    |

|---------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Memory<br>Part                        | SDRAM device<br>model <sup>5</sup> | The models supported by DDR3 include:<br>MT41K128M8XX<br>MT41K64M16XX<br>MT41K256M8XX<br>MT41K128M16XX<br>MT41K512M8XX<br>MT41K512M8XX<br>MT41K256M16XX                                                                                                        | MT41K256<br>M16XX                                                                                   |

|                                       | Create Custom Part                 | Custom new SDRAM type enable selection.<br>If the device models supported by the IP do not meet the<br>requirements, users can check this option and customize<br>a new SDRAM type based on the reference model in the<br>Custom Memory Part option box below. | Cleared                                                                                             |

|                                       | Select Base Part <sup>7</sup>      | Custom SDRAM reference model.                                                                                                                                                                                                                                  | MT41K256<br>M16XX                                                                                   |

| Custom<br>Memory<br>Part <sup>6</sup> | Timing Parameters <sup>8</sup>     | Custom SDRAM Timing parameters, including: trfc,<br>tras, trp, trcd, twr, trefi, trtp, twtr.                                                                                                                                                                   | trfc: 160<br>tras: 36<br>trp: 13.5<br>trcd: 13.5<br>twr: 15<br>trefi: 7.8<br>trtp: 7.5<br>twtr: 7.5 |

|                                       | Row Address <sup>9</sup>           | Row address.                                                                                                                                                                                                                                                   | 14                                                                                                  |

|                                       | Column Address <sup>10</sup>       | Column address.                                                                                                                                                                                                                                                | 10                                                                                                  |

|                                       | Bank Address <sup>11</sup>         | Bank address.                                                                                                                                                                                                                                                  | 3                                                                                                   |

5 The default value for this parameter is related to the "Memory Type," DDR3: MT41K128M16XX; DDR2: MT47H128M16XX-25E; LPDDR: MT46H128M16XXX-5L-IT.

7 The default value for this parameter is related to the "Memory Type," DDR3: MT41K128M16XX; DDR2: MT47H128M16XX-25E; LPDDR: MT46H128M16XXX-5L-IT.

8 The default value for this parameter is related to the "Memory Type," DDR3: 1)trfc: 160, 2) tras: 36, 3)trp: 13.5, 4)trcd: 13.5, 5) twr: 15, 6) trefi: 7.8, 7) trtp: 7.5, 8) twtr: 7.5; DDR2: 1)trfc: 197.5, 2)tras: 40, 3) trp: 12.5, trcd: 12.5, 5)twr: 15, 6) trefi: 7.8, 7) trtp: 7.5, 8) twtr: 7.5; LPDDR: 1)trfc: 72, 2) tras: 38.4, 3) trp: 14.4, 4)trcd: 14.4, 5)twr: 14.4, 6)trefi: 7.8, 7) twtr: 2.

9 The default value for this parameter is related to the "Memory Type", DDR3: 14; DDR2: 14; LPDDR: 14.

10 The default value for this parameter is related to the "Memory Type", DDR3: 10; DDR2: 10; LPDDR: 11.

11 The default value for this parameter is related to the "Memory Type," DDR3: 3; DDR2: 3; LPDDR: 2.

<sup>6</sup> This option box is displayed when the "Create Custom Part" option is selected, and it is used to customize a new SDRAM type.

| Option<br>Domain               | Option<br>Name/Parameter<br>Name   | Parameter Description                                                                                                | Default<br>Value |

|--------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------|

| Drive<br>Options <sup>12</sup> | Output Driver<br>Impedance Control | Drive strength options supported by DDR3. For detailed information, please refer to " <i>JESD79-3D</i> , <i>DDR3</i> | RZQ/6            |

|                                | RTT(nominal)-ODT                   | SDRAM Standard".                                                                                                     | RZQ/4            |

### 2.3.1.2.3 Step 3: Pin/Bank Options

Pin/Bank Options is the configuration page for interface parameters, as shown in Figure 2-8. Please refer to Table 2-4 for detailed parameter descriptions.

| Step 1: Basic Options Step 2: Memor | ry Options Step 3: Pin/Bank Opt                                       | ions Step 4: Summary                                  |                     |

|-------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------|---------------------|

| Memory Pin Constraint File Select   | ;                                                                     |                                                       |                     |

| Please select a fdc file which co   | ontains default memory pins cons                                      | traint.                                               |                     |

| Enable fdc file select              |                                                                       |                                                       |                     |

| PLL Reference Clock Pin Options -   |                                                                       |                                                       |                     |

| Please select the banks for the P   | PLL Reference Clock in the archi                                      | tectural view below.                                  |                     |

| PLL Reference Clock Bank:           | R5 🗸                                                                  |                                                       |                     |

| Control/Address Pin Options         |                                                                       |                                                       |                     |

| Please select the banks for the     | Control/Address in the archited                                       | tural view below.                                     |                     |

| Control/Address Bank:               | R5 🗸                                                                  |                                                       |                     |

|                                     | Control/Address in the architect<br>oled,it should be considered NF : | tural view below.<br>maintained LOW through an extern | al resister to GND) |

| Please select the groups for the    | e Control/Address in the archite                                      | ectural view below.                                   |                     |

| Custom Control/Address Group        |                                                                       |                                                       |                     |

| Data Pin Options                    |                                                                       |                                                       |                     |

| Please select the banks and group   | os for the data in the architect                                      | ural view below.                                      |                     |

| Signal Name                         | Bank Number                                                           | Group Number                                          |                     |

| DQ[0-7]                             | R4 🗸                                                                  | G0 🗸                                                  |                     |

| DQ[8-15]                            | R4 🗸                                                                  | G1 🗸                                                  |                     |

Figure 2-8 Pin/Bank Options Page

<sup>12</sup> The option parameters related to drive strength and their default configurations are associated with the "Memory Type". The drive strength options for different types of SDRAM and their default configurations are described as follows:

DDR3: Output Driver Impedance Control (default configuration: RZQ/6), RTT(nominal)-ODT (default configuration: RZQ/4);

DDR2: Output Driver Strength (default configuration: Full strength), RTT(nominal)-ODT (default configuration: 750hms);

LPDDR: Driver Strength (default configuration: Full strength).

#### Attention:

All configuration items in "Step 3: Pin/Bank Options" must be configured according to the actual pin assignments on the circuit board. After generating the IP, the DQ pins, reset pins and status pins should be constrained according to actual pin assignments on the cuicuit board, otherwise errors may occur during the flow process.

| Option<br>Domain                         | Option<br>Name/Parameter<br>Name   | Parameter Description                                                                                                                                                                                                                                                                                                                                                                   | Default<br>Value |

|------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Memory Pin<br>Constraint<br>File Select  | Enable fdc file select             | Custom .fdc files can be imported.<br>When enabled, users can input the path to their fdc<br>file in the text box. It will automatically read the<br>Memory interface constraints from the fdc file and<br>configure the Control/Address and Data Pins in the<br>UI.<br>Notes: The signal names of the Memory interface in<br>the user's fdc must match those in the Example<br>Design. | Disabled         |

| PLL<br>Reference<br>Clock Pin<br>Options | PLL Reference Bank <sup>13</sup>   | The bank where the PLL reference clock is located.                                                                                                                                                                                                                                                                                                                                      | L5               |

|                                          | Control/Address Bank <sup>13</sup> | The bank where the Memory interface's control and address lines are located.                                                                                                                                                                                                                                                                                                            | L5               |

|                                          | Enable CS_n                        | mem_cs_n signal enable selection.                                                                                                                                                                                                                                                                                                                                                       | Enabled          |

| Control/<br>Address Pin<br>Options       | Custom<br>Control/Address Group    | User-defined control and address bus grouping<br>enable selection.<br>Selected: User defines the grouping and pin<br>constraints for each PAD;<br>Cleared: default grouping.                                                                                                                                                                                                            | Disabled         |

|                                          | Control and address signals        | This option box is displayed when the "Custom<br>Control/Address Group" option is selected, and it is<br>used to select the Group and Pin where the control<br>and address signals corresponding PADs are located.                                                                                                                                                                      | -                |

Table 2-4 Description of Configuration Parameters on Pin/Bank Options Page

<sup>13</sup> The default value for this parameter is related to the selected device and package: PG2L25H: 1) MBG325: L5; PG2L50H: 1) MBG324: L5, 2) FBG484: L4; PG2L100H: 1)FBG484: R5, 2) FBG676: L5, 3) MBG324: R5; PG2T390H: 1) FFBG900: L3, 2) FFBG676: L5; PG2L200H: 1)FBB484: R5, 2) FBB676: L5, 3)FFBG1156: R4; PG2L100HX: 1) FBG484: R5, 2) FBG676: L5, 3) MBG324: R5; PG2K400: 1)FFBG900: L8, 2) FFBG676: L6; PG2T70H: 1)FBB484: L5, 2)FBB676: L5.

| Option<br>Domain | Option<br>Name/Parameter<br>Name | Parameter Description                              | Default<br>Value |

|------------------|----------------------------------|----------------------------------------------------|------------------|

| Data Pin         | Bank Number <sup>14</sup>        | Select the bank where DQ <sup>15</sup> is located. | L6               |

| Options          | Group Number <sup>16</sup>       | Select the group where $DQ^{15}$ is located.       | G1               |

Note: "-" indicates that there is no default value for this parameter in the IP configuration interface.

#### Attention:

For the "Custom Control/Address Group" option, it is recommended to use custom grouping due to different PCB traces in actual use.

When checking the "Custom Control/Address Group" option for custom pin configuration, ensure that signals are not constrained to the same pin. If pins are constrained to the same location, the UI will highlight the corresponding Pin Number in red.

#### 2.3.1.2.4 Step 4: Summary

The Summary page is used to print the current configuration information without configuration required, as shown in Figure 2-9.

<sup>14</sup> The default configuration value of this parameter depends on the selected device and package. For example, for DQ[0-7],

PG2L25H: 1)MBG325: L4; PG2L50H: 1) MBG324: L4, 2) FBG484: L3; PG2L100H: 1)FBG484: R4, 2) FBG676: L6, 3) MBG324:

R4; PG2T390H: 1)FFBG900: L2, 2) FFBG676: L6; PG2L200H: 1)FBB484: R4, 2) FBB676: L6, 3)FFBG1156: R3; PG2L100HX: 1)

FBG484: R4, 2) FBG676: L6, 3) MBG324: R4; PG2K400: 1)FFBG900: L9, 2) FFBG676: L7; PG2T70H: 1)FBB484: L4, 2)

FBB676: L6.

<sup>15</sup> DQ[8-15] is displayed when the data width is greater than 8, DQ[16-23] is displayed when the data width is greater than 16, DQ[24-31] is displayed when the data width is greater than 24, DQ[32-39] is displayed when the data width is greater than 32, DQ[40-47] is displayed when the data width is greater than 40, DQ[48-55] is displayed when the data width is greater than 48, DQ[56-63] is displayed when the data width is greater than 56, DQ[64-71] is displayed when the data width is greater than 64.

<sup>16</sup> The default configuration value of this parameter depends on the selected device and package. For example, for DQ[0-7],

PG2L25H: 1)MBG325: G1; PG2L50H: 1)MBG324: G0, 2)FBG484: G2; PG2L100H: 1) FBG484: G0, 2)FBG676: G1, 3)MBG324:

G2; PG2T 390H: 1)FFBG900: G0, 2)FFBG676: G3; PG2L200H: 1) FBB484: G0, 2)FBB676: G1, 3)FFBG1156: G1; PG2L100HX:

1)FBG484: G0, 2)FBG676: G1, 3)MBG324: G2; PG2K400: 1) FFBG900: G2, 2)FFBG676: G0; PG2T70H: 1)FBB484: G0, 2)

FBB676: G3.

| Step 1: Basic Options Ste | ep 2: Memory Options Step 3: Pin/Bank Options Step 4: Summary |

|---------------------------|---------------------------------------------------------------|

| Basic Options             |                                                               |

| Memory Type               | : DDR3                                                        |

| Operating Mode            | : Controller + PHY                                            |

| Total Data Width          | : 16                                                          |

| Density                   | : 2Gb                                                         |

| Volt                      | : 1.5V                                                        |

| Input Clock Frequency     | : 50MHz                                                       |

| Data Rate                 | : 800.0Mppa                                                   |

| Memory Options            |                                                               |

| Memory Part               | : MT41K120M16XX                                               |

| Row Address               | : 14                                                          |

| Column Address            | : 10                                                          |

| Bank Address              | : 3                                                           |

| Output Driver Impedance   | : Control : RZQ/6                                             |

| RTT (nominal) -ODT        | : RZQ/4                                                       |

| Pin/Bank Options          |                                                               |

| PLL Reference Clock Ban   | 1k : R5                                                       |

| Control/Address Bank      | : R5                                                          |

| CS_n                      | : Enabled                                                     |

| DQ[0-7] Bank              | : R4                                                          |

| DQ[8-15] Bank             | : R4                                                          |

#### 2.3.1.3 Generating IP

After completing the parameter configuration, click the <Generate> button in the top left corner to generate IP and the HMIC\_S IP code corresponding to the user-specific settings. The information report interface for IP generation is shown in Figure 2-10.

Done: 0 error(s), 0 warning(s)

#### Attention:

The .pds and .fdc files generated with the IP are for reference only; please modify the pin constraints according to the actual pin connections when in use.

Upon successful IP generation, the files indicated in Table 2-5 will be output to the Project path specified in Figure 2-3.

| Output File <sup>17</sup>                                                                                                                                             | Description                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| \$instname.v                                                                                                                                                          | The top-level .v file of the generated IP for Controller + PHY.                                                       |

| \$instname_ddrphy_top.v                                                                                                                                               | The top-level .v file of the generated IP for PHY.                                                                    |

| \$instname.idf The Configuration file of the generated IP.                                                                                                            |                                                                                                                       |

| /rtl/*                                                                                                                                                                | The RTL code file of the generated IP.                                                                                |

| /example_design/*                                                                                                                                                     | The Test Bench and the corresponding Memory Simulation Model files used<br>by the Example Design of the generated IP. |

| /pnr/*                                                                                                                                                                | The project files .pds and pin constraint files .fdc for the Example Design of the generated IP.                      |

| /sim/* The simulation directory for the generated IP. sim.tcl is a ModelS simulation script, makefile is a VCS simulation script, and sim_filist of simulation files. |                                                                                                                       |

| /sim_lib/*                                                                                                                                                            | The directory of the encryption files for the IP.                                                                     |

| /rev_1 The default output path for synthesis reports. (This folder is gen after specifying the synthesis tool)                                                        |                                                                                                                       |

| readme.txt The readme file describes the structure of the generation directory is generated.                                                                          |                                                                                                                       |

Table 2-5 Output Files after IP Generation

# 2.3.2 Constraint Configuration

For the specific configuration method of constraint files, please refer to the relevant help documents in the PDS installation path: "User\_Constraint\_Editor\_User\_Guide", "Physical\_Constraint\_Editor\_User\_Guide", and "Route\_Constraint\_Editor\_User\_Guide".

# 2.3.3 Simulation Runs

The simulation of HMIC\_S IP is based on the Test Bench of the Example Design. For detailed information about Example Design, please refer to "2.4 Example Design".

For more details about the PDS simulation functions and third-party simulation tools, please consult the related help documents in the PDS installation path: "*Pango\_Design\_Suite\_User Guide*", "*Simulation\_User\_Guide*".

<sup>17 &</sup>lt;\$instname> is the instantiation name entered by the user; "\*" is a wildcard character used to replace files of the same type.

### 2.3.3.1 ModelSim Simulation

Simulation operation steps: Open cmd.exe, switch the current directory to "/sim/modelsim" under the IP generation directory in the command line, run vsim (vsim-64 is used on the server), and open the ModelSim simulation software, as shown in Figure 2-11.

Figure 2-11 Open ModelSim Instruction

Run the ctrl\_phy\_sim.tcl script in the ModelSim simulation software to perform simulation, as shown in Figure 2-12.

# 2.3.3.2 VCS simulation

Enter the "sim/vcs" directory in Terminal, type "make" and press "Enter" to start the simulation, as shown in Figure 2-13.

□ ×

File Edit View Search Terminal Help TCSERVER35{dingwei}:[/localhome/design\_temp/dingw/PG2L/PG2L100H/pg2l\_ddr/sim\_vcs/ddr3\_1066x16\_sim\_test/sim/vcs]% ll total 20 -rw-r----. 1 dingwei AE\_IP 541 Sep 24 14:37 makefile -rw-r----. 1 dingwei AE\_IP 15023 Sep 24 11:04 sim file\_list.f TCSERVER35{dingwei}:[/localhome/design\_temp/dingw/PG2L/PG2L100H/pg2l\_ddr/sim\_vcs/ddr3\_1066x16\_sim\_test/sim/vcs]% make

Figure 2-13 VCS Simulation Script Execution

2.3.4 Synthesis and Placement/Routing

The specific usage of PDS synthesis tools and placement/routing tools can be found in the help documents within the PDS installation path.

#### Attention:

Example Design project file .pds and pin constraint file .fdc generated with the IP are located in the "/pnr/" directory, and physical constraints need to be modified according to the actual devices and PCB trace routing. For details, please refer to "2.8 Descriptions and Considerations".

# 2.3.5 Resources Utilization

| Deries    | Configuration | ID On sucting Made                 | Typical Resource Utilization Values |      |      |      |      |

|-----------|---------------|------------------------------------|-------------------------------------|------|------|------|------|

| Device    | Mode          | IP Operating Mode                  | LUT                                 | FF   | GPLL | PPLL | USCM |

| PG2L25H   | DDR3 x32      | Controller + PHY                   | 4208                                | 4094 | 2    | 2    | 2    |

| PG2L50H   | DDR3 x32      | Controller + PHY                   | 4200                                | 4094 | 2    | 2    | 2    |

|           | DDR3 x32      | Controller + PHY                   | 4711                                | 4179 | 2    | 2    | 2    |

| PG2L100H  | DDR3 x64      | Controller + PHY                   | 6885                                | 5794 | 2    | 3    | 2    |

|           | DDR3 x32      | Controller + PHY,<br>Standard AXI4 | 7042                                | 9214 | 2    | 2    | 2    |

| PG2L100HX | DDR3 x32      | Controller + PHY                   | 4290                                | 4148 | 2    | 2    | 2    |

| DDR3 x64  |               | Controller + PHY                   | 6479                                | 5732 | 2    | 3    | 2    |

| PG2L200H  | DDR3 x32      | Controller + PHY                   | 4209                                | 4094 | 2    | 2    | 2    |

| PO2L200H  | DDR3 x64      | Controller + PHY                   | 6274                                | 5676 | 2    | 3    | 2    |

| DC2T200U  | DDR3 x16      | Controller + PHY                   | 3528                                | 3373 | 2    | 2    | 2    |

| PG2T390H  | DDR3 x32      | Controller + PHY                   | 4703                                | 4183 | 2    | 2    | 2    |

| DC2K400   | DDR3 x32      | Controller + PHY                   | 4260                                | 4150 | 2    | 2    | 2    |

| PG2K400   | DDR3 x64      | Controller + PHY                   | 6356                                | 5734 | 2    | 3    | 2    |

Table 2-6 Typical Resource Utilization Values for HMIC\_S IP Based on Applicable Devices

| Device    | Configuration | IP Operating Mode                    | Typical Resource Utilization Values |      |      |      |      |

|-----------|---------------|--------------------------------------|-------------------------------------|------|------|------|------|

| Device    | Mode          |                                      | LUT                                 | FF   | GPLL | PPLL | USCM |

| PG2T70H   | DDR3 x32      | Controller + PHY                     | 4171                                | 4148 | 2    | 2    | 2    |

| DDR3 x64  |               | Controller + PHY                     | 6235                                | 5730 | 2    | 3    | 2    |

| DCOTOOLIX | DDR3 x32      | Controller + PHY                     | 4262                                | 4094 | 2    | 2    | 2    |

| PG2T390HX | DDR3 x64      | Controller + PHY                     | 6343                                | 5676 | 2    | 3    | 2    |

| PG2T160H  | DDR3x32       | Controller + PHY,<br>Simplified AXI4 | 4288                                | 4233 | 2    | 2    | 2    |

| г021100П  | DDR3x32       | Controller + PHY,<br>Standard AXI4   | 6360                                | 8578 | 2    | 2    | 2    |

# 2.4 Example Design

This section mainly introduces the Example Design scheme based on HMIC\_S IP (Controller + PHY mode). In this scheme, the user logic acts as AXI Master with the HMIC\_S IP as AXI Slave. The user logic writes data through the Write channel of the AXI interface and receives data through the Read channel for data comparison. If there is a data error, the Error LED will light up.

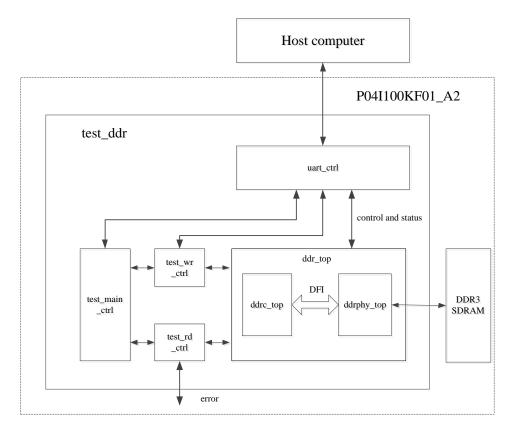

# 2.4.1 Design Block Diagram

Figure 2-14 Example Design System Block Diagram

The system block diagram of the Example Design is shown in Figure 2-14, where test\_main\_ctrl is the control module for AXI read and write instructions, test\_wr\_ctrl is the control module for AXI write instructions and data writing, test\_rd\_ctrl is the control module for AXI read instructions and data reading, and uart\_ctrl is the serial port conversion module for easy control and internal state reading during debugging.

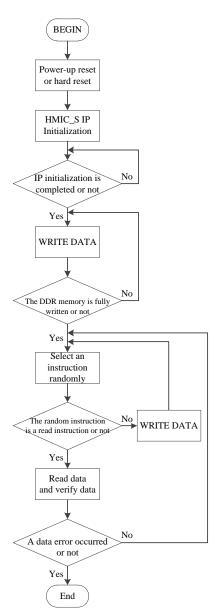

# 2.4.2 Test Method

In the Example Design, the user logic performs read and write operations on HMIC\_S IP and checks the readback data. The detailed test process is as shown in Figure 2-15.

Figure 2-15 Example Design Test Flowchart

After the system is powered up or a hard reset is initiated, the HMIC\_S IP begins initialization. Once initialization is completed (indicated by the ddrc\_init\_done signal going high), the test\_main\_ctrl module controls the test\_wr\_ctrl module to generate write instructions and write data to initialize the DDR chips. After write full, test\_main\_ctrl starts random read and write operations, and test\_rd\_ctrl checks the readback data to determine if there are any errors.

#### Attention:

Do not directly use the Example Design generated by the IP for on-board testing flow. Constrain pins according to the actual pin connections of the board, then proceed with Flow on-board testing.

# **2.5 Descriptions of IP Interfaces**

This section provides the HMIC\_S IP related interface instructions and timing descriptions.

# 2.5.1 Controller Interface Description

#### 2.5.1.1 Global Interface

| Port          | I/O | Bit width | Valid Values | Description                                                                                                                                                                                |

|---------------|-----|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk           | Ι   | 1         | -            | External clock input.                                                                                                                                                                      |

| rst_n         | Ι   | 1         | Low          | External reset input.                                                                                                                                                                      |

| phy_init_done | Ι   | 1         | High         | Initialization completion flag for ddrphy:<br>1'b1: ddrphy initialization is complete;<br>1'b0: DDRPHY initialization is incomplete;                                                       |

| ddr_init_done | 0   | 1         | High         | Initialization completion flag for the IP:<br>1'b1: ddr IP initialization is complete;<br>1'b0: ddr IP initialization is incomplete, and<br>external operations on the ddr IP are invalid. |

Table 2-7 Global Interface

Note: "-" indicates that the parameter does not exist.

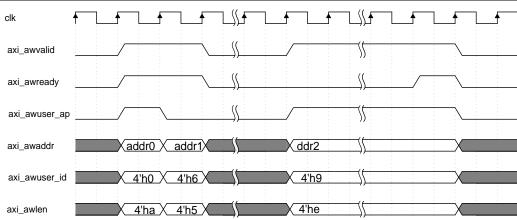

# 2.5.1.2 Simplified AXI4 interface

# 2.5.1.2.1 Write address channel

| Port          | I/O | Bit width       | Valid Values | Description                    |

|---------------|-----|-----------------|--------------|--------------------------------|

| axi_awaddr    | Ι   | CTRL_ADDR_WIDTH | -            | AXI write address.             |

| axi_awuser_ap | Ι   | 1               | High         | AXI write with auto precharge. |

| axi_awuser_id | Ι   | 4               | -            | AXI write address ID.          |

| axi_awlen     | Ι   | 4               | -            | AXI burst length for writing.  |

| axi_awready   | 0   | 1               | High         | AXI write address ready.       |

| axi_awvalid   | Ι   | 1               | High         | AXI write address valid.       |

Note: "-" indicates that the parameter does not exist.

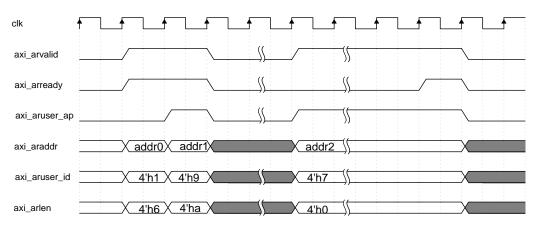

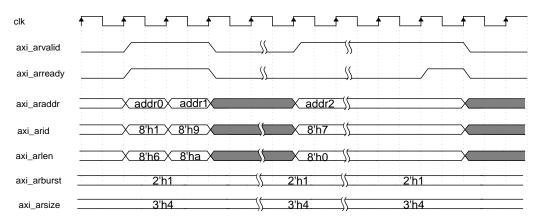

#### 2.5.1.2.2 Read address channel

| Table 2-9 Read Address Channel |

|--------------------------------|

|--------------------------------|

| Port          | I/O | Bit width       | Valid Values | Description                   |

|---------------|-----|-----------------|--------------|-------------------------------|

| axi_araddr    | Ι   | CTRL_ADDR_WIDTH | -            | AXI read address.             |

| axi_aruser_ap | Ι   | 1               | High         | AXI read with auto precharge. |

| axi_aruser_id | Ι   | 4               | -            | AXI read address ID.          |

| axi_arlen     | Ι   | 4               | -            | AXI burst length for reading. |

| axi_arready   | 0   | 1               | High         | AXI read address ready.       |

| axi_arvalid   | Ι   | 1               | High         | AXI read address valid        |

Note: "-" indicates that the parameter does not exist.

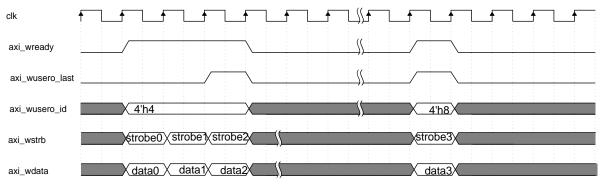

# 2.5.1.2.3 Write data channel

| Table 2-10 | Write Data | Channel |

|------------|------------|---------|

|------------|------------|---------|

| Port            | I/O | Bit width    | Valid Values | Description             |

|-----------------|-----|--------------|--------------|-------------------------|

| axi_wdata       | Ι   | DQ_WIDTH*8   | -            | AXI write data.         |

| axi_wstrb       | Ι   | DQ_WIDTH*8/8 | High         | AXI write data strobes. |

| axi_wready      | 0   | 1            | High         | AXI write data ready.   |

| axi_wusero_id   | 0   | 4            | -            | AXI write data ID.      |

| axi_wusero_last | 0   | 1            | High         | AXI write data last.    |

Note: "-" indicates that the parameter does not exist.

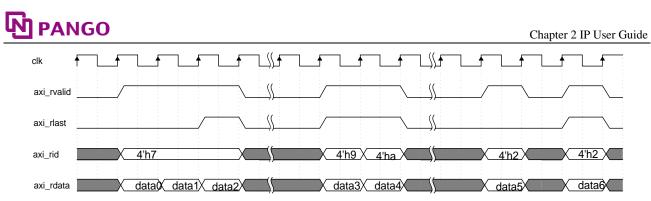

# 2.5.1.2.4 Read data channel

| Port       | I/O | Bit width  | Valid Values | Description                |

|------------|-----|------------|--------------|----------------------------|

| axi_rid    | 0   | 4          | -            | AXI read data ID.          |

| axi_rlast  | 0   | 1          | High         | AXI read data last signal. |

| axi_rvalid | 0   | 1          | High         | AXI read data valid.       |

| axi_rdata  | 0   | DQ_WIDTH*8 | -            | AXI read data.             |

Table 2-11 Read Data Channel

Note: "-" indicates that the parameter does not exist.

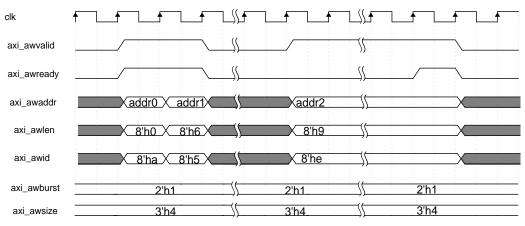

### 2.5.1.3 Standard AXI4 Interface

### 2.5.1.3.1 Write address channel

| Table 2-12 Write Address Chan |

|-------------------------------|

|-------------------------------|

| Port        | I/O | Bit width      | Valid Values | Description                   |

|-------------|-----|----------------|--------------|-------------------------------|

| axi_awaddr  | Ι   | AXI_ADDR_WIDTH | -            | AXI write address.            |

| axi_awid    | Ι   | 8              | -            | AXI write address ID.         |

| axi_awsize  | Ι   | 3              | -            | AXI write burst size.         |

| axi_awburst | Ι   | 2              | -            | AXI write burst type.         |