# Logos2 Family FPGAs Analog-to-Digital Converter (ADC) ModuleUser Guide

(UG040009, V1.6) (19.07.2023)

Shenzhen Pango Microsystems Co., Ltd. All Rights Reserved. Any infringement will be subject to legal action.

### **Revisions History**

#### **Document Revisions**

| Version | Date of Release | Revisions        |  |

|---------|-----------------|------------------|--|

| V1.6    | 19.07.2023      | Initial release. |  |

|         |                 |                  |  |

### **About this Manual**

#### **Terms and Abbreviations**

| Terms and Abbreviations | Meaning                           |  |

|-------------------------|-----------------------------------|--|

| ADC                     | Analog to Digital Converter       |  |

| SAR                     | Successive Approximation Register |  |

| N/A                     | Not Applicable                    |  |

| DRP                     | Dynamic Reconfiguration Port      |  |

| MSPS                    | Mega Sample Per Second            |  |

| APB                     | Advanced Peripheral Bus           |  |

| JTAG                    | Joint Test Action Group           |  |

| JDRP                    | JTAG Dynamic Reconfiguration Port |  |

| FS                      | Full-Scale                        |  |

| LSB                     | Least Significant Bit             |  |

| ОТ                      | Over Temperature                  |  |

| IOB                     | Input Output Buffer               |  |

|                         |                                   |  |

### **Table of Contents**

| Revisions History                                            |    |

|--------------------------------------------------------------|----|

| About this Manual                                            | 2  |

| Table of Contents                                            |    |

| Tables                                                       |    |

| Figures                                                      | 5  |

| Chapter 1 General Introduction                               | 6  |

| Chapter 2 Detailed Introduction                              | 7  |

| 2.1 ADC Structure Block Diagram                              | 7  |

| 2.2 Features                                                 | 7  |

| 2.3 ADC Port Description                                     | 8  |

| 2.4 ADC Analog Input                                         | 10 |

| 2.5 ADC Signal Conversion                                    |    |

| 2.6 Temperature Monitoring                                   | 13 |

| 2.6.1 Over-temperature Alarm Function                        | 14 |

| 2.6.2 Temperature Calibration Function                       | 15 |

| 2.7 Supply Voltage Monitoring                                | 16 |

| 2.8 Register Description                                     | 17 |

| 2.8.1 Control Registers                                      |    |

| 2.8.2 Status Registers                                       | 25 |

| 2.9 ADC Operating Modes                                      |    |

| 2.9.1 Power-up Mode                                          |    |

| 2.9.2 Sequential Scanning Mode                               |    |

| 2.10 JTAG and APB Interfaces of the ADC                      |    |

| 2.10.1 ADC JTAG Read/Write Timing                            |    |

| 2.10.2 ADC APB Read/Write Timing                             |    |

| 2.10.3 Description of Sampling and APB Read Tme in User Mode |    |

| Disclaimer                                                   |    |

## PANGO

### Tables

| Table 1-1 Logos2 Family FPGA ADC Pin Description                                  | 6  |

|-----------------------------------------------------------------------------------|----|

| Table 2-1 List of ADC Features                                                    | 7  |

| Table 2-2 GTP_ADC_E2 Port List                                                    | 8  |

| Table 2-3 ADC Analog Input Signals                                                | 11 |

| Table 2-4 Typical Voltage Monitored by Voltage Sensor                             | 16 |

| Table 2-5 Control Register Address Description                                    | 18 |

| Table 2-6 Configuration Register List                                             | 19 |

| Table 2-7 OT Signal Debounce Counter                                              | 21 |

| Table 2-8 Clock Division Control                                                  | 21 |

| Table 2-9 Sequence Register List                                                  | 22 |

| Table 2-10 Sequence Register Dedicated Channel Bit Mapping Relationship           | 24 |

| Table 2-11 Alarm Register List                                                    | 24 |

| Table 2-12 Status Register List                                                   | 25 |

| Table 2-13 JTAG Operation Instructions                                            | 31 |

| Table 2-14 Clock Division and DCLK Frequency That Meet Data Sampling Requirements | 34 |

## PANGO

## Figures

| Figure 2-1 ADC Structure Block Diagram                                               | .7  |

|--------------------------------------------------------------------------------------|-----|

| Figure 2-2 GTP_ADC_E2 Interface Diagram                                              | .8  |

| Figure 2-3 Timing Diagram of LOADSC_N Signal and DCLK/clk_osc                        | .9  |

| Figure 2-4 Unipolar Mode Input Diagram1                                              | 0   |

| Figure 2-5 Bipolar Mode Pseudo-Differential Input Diagram1                           | 1   |

| Figure 2-6 Bipolar Mode True Differential Input Diagram 1                            | 1   |

| Figure 2-7 ADC Analog-to-Digital Conversion Chart in Unipolar Mode1                  | 2   |

| Figure 2-8 ADC Analog-to-Digital Conversion Chart in Bipolar Mode1                   | 3   |

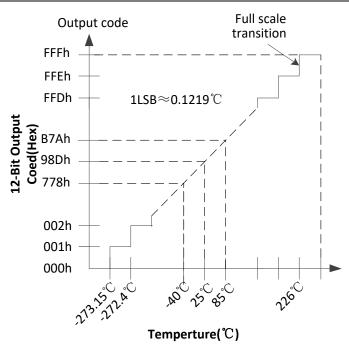

| Figure 2-9 Temperature Sensor Conversion Characteristics1                            | 4   |

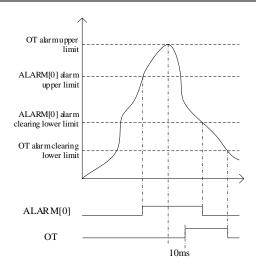

| Figure 2-10 Overview of Over-temperature Alarm Function1                             | 5   |

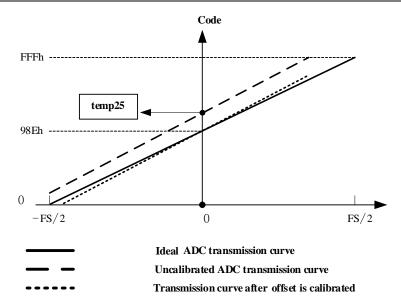

| Figure 2-11 Temperature Offset Calibration Diagram1                                  | 6   |

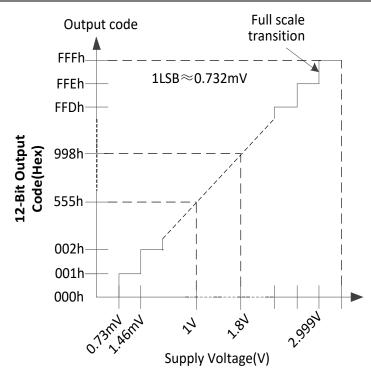

| Figure 2-12 Ideal Voltage Sensor Conversion Characteristics1                         | 7   |

| Figure 2-13 Register Interface1                                                      | 8   |

| Figure 2-14 Configuration Register Bit Allocation1                                   | 9   |

| Figure 2-15 Sequence Register Bit Allocation                                         | 22  |

| Figure 2-16 Alarm Register Bit Allocation2                                           | 24  |

| Figure 2-17 Status Register Data Structure Diagram2                                  | 26  |

| Figure 2-18 ADC Analog-to-Digital Conversion Timing Diagram                          | 27  |

| Figure 2-19 Timing Diagram for ADC_A/B Power-down then Power-up                      | 28  |

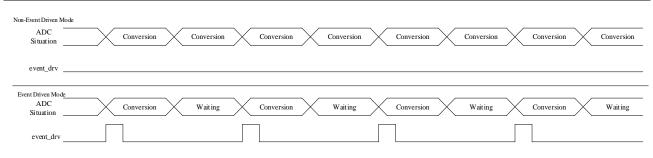

| Figure 2-20 Function of the event_drv Signal in Event-driven Mode                    | 30  |

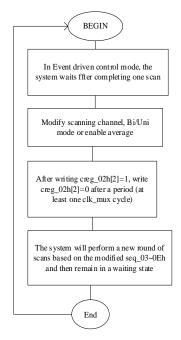

| Figure 2-21 Flowchart for Modifying Sequence Register Functions in Event-driven Mode | 30  |

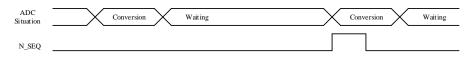

| Figure 2-22 N_SEQ Function Implementation Flow and Waveform Diagram                  | 30  |

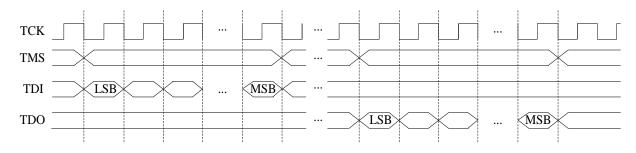

| Figure 2-23 JTAG DRP Timing Diagram                                                  | \$2 |

| Figure 2-24 APB Write Register Timing Diagram                                        | \$2 |

| Figure 2-25 APB Read Register Timing Diagram                                         | 3   |

#### **Chapter 1 General Introduction**

The Logos2 Family FPGA products provide an Analog-to-Digital Converter (ADC) module which includes two 12-bit SAR-ADC resources. The two ADC resources share up to 17 pairs of external input ports, including 16 pairs of analog input pins multiplexed with IOB and 1 pair of dedicated analog input pin. The scanning of 17 pairs of external input ports is flexibly controlled by the FPGA. Users can read and write the ADC's control register and read the ADC's status register through user logic. Meanwhile, the ADC can also monitor 4 sets of internal voltages in real-time, and the built-in temperature sensor can detect the chip junction temperature (Tj) in real-time, outputting overtemperature alarms based on preset thresholds. Below are some parameters of the ADC:

- Resolution: 12-bits;

- Sample rate: 1MSPS;

- Up to 17 pairs of external analog channels, including 16 pairs of analog input channels multiplexed with IOB and 1 pair of dedicated analog input channel (refer to the respective package manual for details)

- > Internal and external reference voltage supported

- Integrated temperature sensor

- Integrated power supply sensor

- For detailed ADC characteristics parameters, please refer to the ADC section in the "DS04001 Logos2 Family FPGA Device Data Sheet"

ADC Module Analog Pin Description:

| Pin Name                    | Pin Type           | Pin Description                                                                                                                                                                                                   |  |

|-----------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VCCADC                      | Dedicated          | ADC analog power supply 1.8V, connected to VCCA when ADC is not used                                                                                                                                              |  |

| VSSADC                      | Dedicated          | ADC AGND, connected to VSS when ADC is not used                                                                                                                                                                   |  |

| VAADC_P                     | Dedicated          | ADC dedicated analog differential input (Positive), left floating or connected to VSS when ADC is not used                                                                                                        |  |

| VAADC_N                     | Dedicated          | ADC dedicated analog differential input (Negative), left floating or connected to VSS when ADC is not used                                                                                                        |  |

| VREFADC_P                   | Dedicated          | 1.255V reference voltage input, connected to VSS when not in use                                                                                                                                                  |  |

| VREFADC_N                   | Dedicated          | 1.255V reference ground input, connected to VSS when not in use                                                                                                                                                   |  |

| VAA[0,,15]P,<br>VAA[0,,15]N | Multi-func<br>tion | Multiplexed ADC differential analog input channels 0-15                                                                                                                                                           |  |

| TSDP                        | Dedicated          | Anode pin of the temperature sensor diode; when the temperature diode is not<br>used, connect to VSS; if the temperature sensor diode is used, an appropriate<br>external temperature monitoring chip is required |  |

| TSDN                        | Dedicated          | Cathode pin of the temperature sensor diode; when the temperature diode is not used, connect to VSS                                                                                                               |  |

Table 1-1 Logos2 Family FPGA ADC Pin Description

#### **Chapter 2 Detailed Introduction**

#### 2.1 ADC Structure Block Diagram

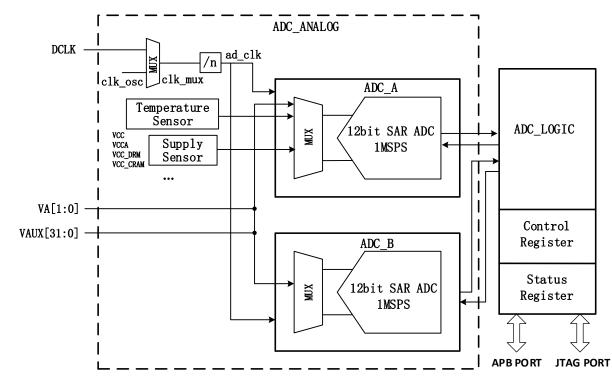

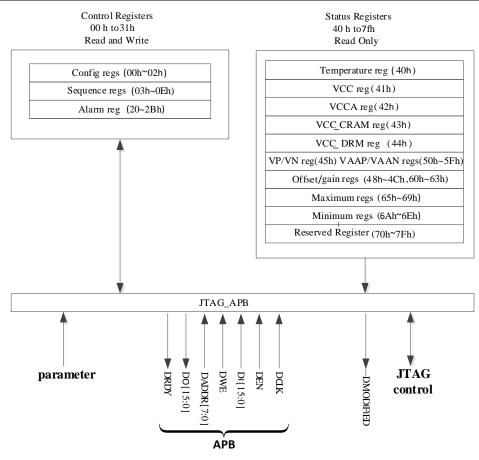

Figure 2-1 ADC Structure Block Diagram

The ADC includes up to 17 pairs of user-connectable analog input channels (where VAUX[31:0] is multiplexed with IOB and VA[1:0] are dedicated analog input channels). VAUX[1] and VAUX[0] correspond to the P and N sides of channel 0, so VAUX[31] and VAUX[30] correspond to the P and N sides of channel 15. For specific ports and description, please refer to Table 2-2 GTP\_ADC\_E2 Port List.

In Figure 2-1, the ADC\_ANALOG module samples the analog input signal, converts it into 12-bit data, and transmits it to the ADC\_LOGIC module. Users can read and write registers in ADC\_LOGIC through the APB interface to control the ADC's working mode and read the ADC's status and conversion values.

#### **2.2 Features**

Table 2-1 List of ADC Features

| Function | Description |

|----------|-------------|

|          |             |

| Function                            | Description                                                                         |  |

|-------------------------------------|-------------------------------------------------------------------------------------|--|

| Access registers via JTAG           | Users can access and operate registers via JDRP                                     |  |

| Access registers via APB            | Users can access and operate registers via APB                                      |  |

| Error calibration                   | Calibrate the ADC conversion values, including offset errors and gain errors        |  |

| Chip monitoring                     | Monitor several on-chip power supply voltages and on-chip temperatures              |  |

| Channel Scan                        | Sequentially scan and convert multiple ADC channels                                 |  |

| Unipolar and Bipolar mixed scanning | The channels scanned by the ADC can be arbitrarily selected as unipolar, or bipolar |  |

| Result averaging                    | The ADC can average the obtained results                                            |  |

| User event-driven                   | Users can control the sampling of the ADC through event-driven control              |  |

| Single channel control              | Users can arbitrarily select a channel for individual configuration                 |  |

| Chip monitoring during programming  | Monitor the chip's voltage and temperature during programming                       |  |

#### **2.3 ADC Port Description**

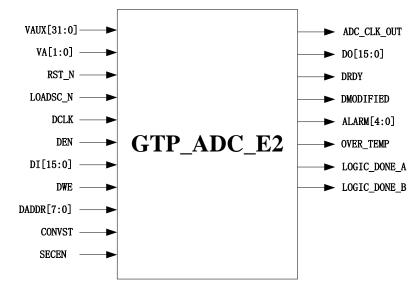

Figure 2-2 GTP\_ADC\_E2 Interface Diagram

The list of ADC GTP ports is as follows:

Table 2-2 GTP\_ADC\_E2 Port List

| Port Name  | I/O                                                                                                                 | Description                                                                                                                                                                                                                    |

|------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VA[1:0]    | A[1:0] I Dedicated analog input ports<br>VA[1] and VA[0] form a differential pair, VA[0]<br>and VA[1] is the P side |                                                                                                                                                                                                                                |

| VAUX[31:0] | Ι                                                                                                                   | Multiplexed analog differential input ports (Multiplexing IOB);<br>IOB must be constrained to 1.8V power standard, and<br>VAUX[2*n+1] and VAUX[2*n] form a differential pair,<br>corresponding to the P and N sides of port n. |

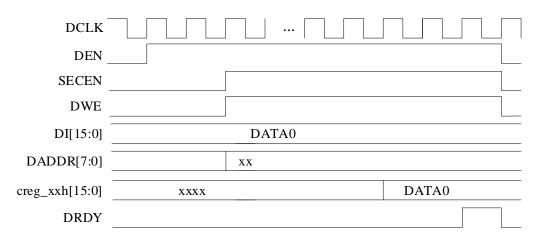

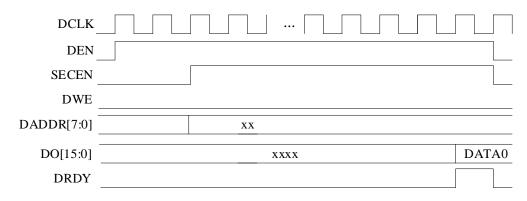

| DCLK       | Ι                                                                                                                   | APB interface clock                                                                                                                                                                                                            |

| DADDR[7:0] | Ι                                                                                                                   | APB operation address bit                                                                                                                                                                                                      |

| Port Name     I/O     Description                                                                                                                                                                                                                                         |   | Description                                                                                                                                                                                                                                                                                                                 |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SECEN                                                                                                                                                                                                                                                                     | Ι | Operation enable; initiates a read/write operation when active high                                                                                                                                                                                                                                                         |  |

| DEN                                                                                                                                                                                                                                                                       | Ι | Data transfer enable signal                                                                                                                                                                                                                                                                                                 |  |

| DWE                                                                                                                                                                                                                                                                       | Ι | Write operation enable: 0 for read, 1 for write                                                                                                                                                                                                                                                                             |  |

| DI[15:0]                                                                                                                                                                                                                                                                  | Ι | APB data input                                                                                                                                                                                                                                                                                                              |  |

| DO[15:0]                                                                                                                                                                                                                                                                  | 0 | APB data output                                                                                                                                                                                                                                                                                                             |  |

| DRDY                                                                                                                                                                                                                                                                      | 0 | APB read/write complete flag                                                                                                                                                                                                                                                                                                |  |

| CONVST                                                                                                                                                                                                                                                                    | Ι | Event-driven control signal, which triggers sampling in event-drive mode                                                                                                                                                                                                                                                    |  |

| RST_N                                                                                                                                                                                                                                                                     | Ι | System reset signal, active-low                                                                                                                                                                                                                                                                                             |  |

| OVER_TEMP                                                                                                                                                                                                                                                                 | 0 | OT (over temperature) indicator signal                                                                                                                                                                                                                                                                                      |  |

| LOGIC_DONE_A                                                                                                                                                                                                                                                              | 0 | ADC status register update signal                                                                                                                                                                                                                                                                                           |  |

| LOGIC_DONE_B                                                                                                                                                                                                                                                              | 0 | ADC status register update signal                                                                                                                                                                                                                                                                                           |  |

| LOADSC_N                                                                                                                                                                                                                                                                  | Ι | Enable control register loaded into static configuration value<br>signal, active low Triggers internal reconfiguration of the ADC<br>control register. For specific usage, please refer to Figure 2-3                                                                                                                       |  |

| ADC_CLK_OUT                                                                                                                                                                                                                                                               | 0 | ADC working clock ad_clk output port                                                                                                                                                                                                                                                                                        |  |

| DMODIFIED O register has been written by JTAG and the user has performed APB operation. After JTAG completes to operation, the DMODIFIED signal is pulled high.                                                                                                           |   | Control register modification flag, indicating that the control<br>register has been written by JTAG and the user has not yet<br>performed APB operation. After JTAG completes the write<br>operation, the DMODIFIED signal is pulled high. The<br>subsequent APB read/write operations will reset the<br>DMODIFIED signal. |  |

| ALARM[4:0]       Alarm indicator signal         ALARM[0] is the temperature alarm signal;         ALARM[1] is the VCC alarm signal;         ALARM[2] is the VCC_alarm signal;         ALARM[3] is the VCC_CRAM alarm signal;         ALARM[4] is the VCC_DRM alarm signal |   | ALARM[0] is the temperature alarm signal;<br>ALARM[1] is the VCC alarm signal;<br>ALARM[2] is the VCCA alarm signal;<br>ALARM[3] is the VCC_CRAM alarm signal;                                                                                                                                                              |  |

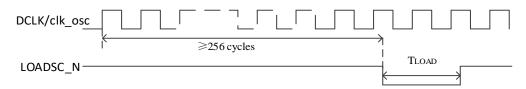

Note: The timing of the LOADSC\_N signal is shown in the following diagram:

Figure 2-3 Timing Diagram of LOADSC\_N Signal and DCLK/clk\_osc

After at least 256 stable clock cycles, the LOADSC\_N signal must held low for two or more clock cycles before pulling high, as shown in Figure 2-3.

The ADC clock can be selected through configuration registers. For details, please refer to CLKSW control bits.

When the ADC uses DCLK, the LOADSC\_N signal must be pulled low to trigger ADC configuration loading. The time  $T_{LOAD}$  for which LOADSC\_N is held low must be at least 2 DCLK cycles.

When the ADC uses internal clk\_osc, the ADC configuration can be automatically loaded; if

reloading is needed, LOADSC\_N must be pulled low for a time T<sub>LOAD</sub> of at least 80ns.

#### 2.4 ADC Analog Input

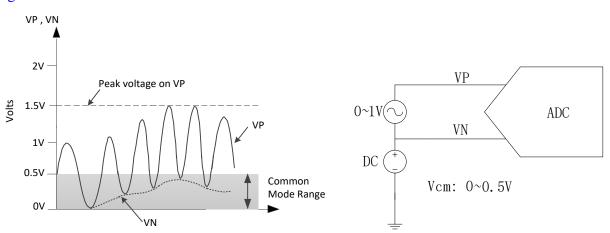

The ADC analog input uses differential sampling to reduce the impact of common-mode noise. All analog input channels are inherently differential, requiring the positive input (VP) and negative input (VN) of the ADC to be driven in differential mode.

When using dedicated ADC channels, the corresponding pins do not need to be constrained. Multi-function analog channel (VAUX[31:0]) pins are shared with general IO. When using multi-function analog channels, these pins cannot be used as general IO and must be constrained to the 1.8V level standard. Unused multiplexed analog channel pins can be used as general IO.

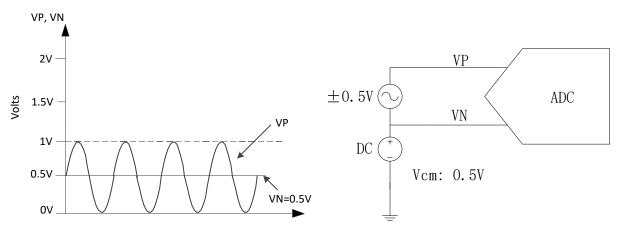

When detecting all on-chip sensors, the ADC operates in Unipolar mode; users may configure external analog input channels in either Unipolar or Bipolar mode. The Unipolar mode is shown in Figure 2-4:

Figure 2-4 Unipolar Mode Input Diagram

In Unipolar mode, VP $\geq$ VN, VN input range is 0–0.5V, and 0V $\leq$ VP–VN $\leq$ 1V.

## PANGO

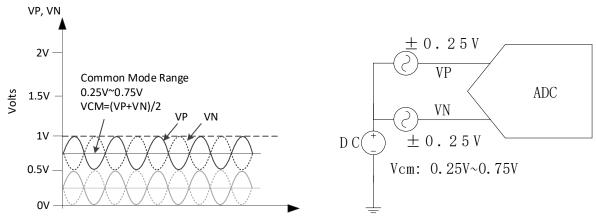

The bipolar mode includes pseudo-differential and true differential, each illustrated in Figure 2-5,

#### Figure 2-6:

Figure 2-5 Bipolar Mode Pseudo-Differential Input Diagram

Figure 2-6 Bipolar Mode True Differential Input Diagram

To ensure proper conversion, the signal requirements for the above input modes are as follows:

| Table 2-3 ADC Analog  | Input Signals |

|-----------------------|---------------|

| Table 2-5 ADC Allalog | input Signais |

| Mode                                     | VP           | VN           |

|------------------------------------------|--------------|--------------|

| Unipolar                                 | VN~(VN+1V)   | 0~0.5V       |

| Bipolar (pseudo-differential)            | 0~1V         | 0.5V         |

| Bipolar (true differential) <sup>1</sup> | Vcm+(±0.25V) | Vcm-(±0.25V) |

Note:

1. Vcm refers to the common-mode voltage of the external input signal.

The mode configuration of different channels is implemented through the sequence register. For details, please refer to Table 2-9 Sequence Register List.

#### 2.5 ADC Signal Conversion

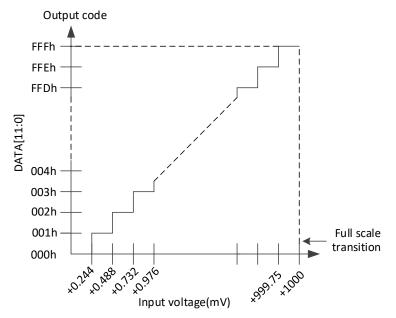

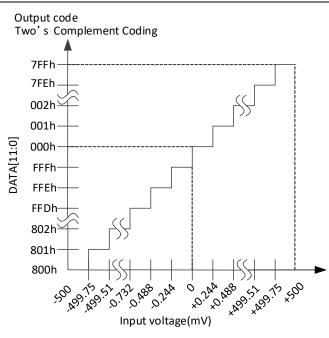

The ADC can operate in different modes (Unipolar, Bipolar) with a default full-scale (FS) of 1V (non-adjustable). If various errors (including Offset error and Gain error) are not considered, the ADC conversion characteristics are as shown in the figure below:

Figure 2-7 ADC Analog-to-Digital Conversion Chart in Unipolar Mode

Figure 2-7 shows the conversion curve under the measurement range of 0 to +1V (FS=1V) in unipolar mode. In this mode, the conversion code is an unsigned number, and LSB=1V/4096=0.244mV. Since the input channels are differential, the VP and VN terminals require differential signal driving. When the input voltage (VP-VN) is 0V, the output code is 000h (if Vp<Vn, then the output is 000h); when the input voltage (VP-VN) is 1V, the output code is FFFh (if Vp-Vn>1V, the output is FFFh).

Figure 2-8 ADC Analog-to-Digital Conversion Chart in Bipolar Mode

Figure 2-8 shows the conversion curve in bipolar mode with a measurement range of -0.5V to +0.5V (FS=1V), where LSB=1V/4096=0.244mV. In this mode, the ADC conversion code is output as a two's complement. When the input voltage (VP-VN) is -500mV, the output code is 800h (the output is 800h when VP-VN< -500mV); when the input voltage is 0V (VP-VN=0V), the output code is 000h; when the input voltage (VP-VN) is +500mV, the output code is 7FFh (the output is 7FFh when VP-VN>500mV).

#### 2.6 Temperature Monitoring

The ADC provides on-chip temperature monitoring function, with temperature detection achieved by measuring the voltage difference between two differently biased PN junctions. Its output voltage is:

$$V_{temp} = 6 * \ln(48) * \frac{kT}{q}$$

$k = 1.38 \times 10^{-23} J/K$  denotes the Boltzmann constant

T = C + 273.15 denotes temperature in Kelvin

$q = 1.6 \times 10^{-19}C$  is electronic charge

When the temp sensor is operating, ADC\_A samples the voltage output from the temp sensor by default; As a backup ADC, ADC-B does not perform sampling on the temp sensor; the ADC defaults to operating in Unipolar mode at this time, storing the conversion results at the 40h address bit in the status register.

Figure 2-9 Temperature Sensor Conversion Characteristics

The temperature sensor inputs a voltage that is linearly related to the temperature to the ADC, converting it into an ADC output code, as shown in the figure above.

The on-chip temperature corresponding to the ADC output code is:

Temperature(  $^{\circ}$ C) = ADC Code \* 0.1219 – 273.15 (The ADC code is represented in hexadecimal format)

#### 2.6.1 Over-temperature Alarm Function

When the internal temperature sensor reading exceeds the upper limit set in the alarm control register creg\_20h, the ALARM [0] signal pulls high from 0 to 1 until the detected temperature value drops below the lower limit set in creg\_21h, at which point the ALARM [0] signal pulls down from 1 to 0. The OT (over\_temperature) signal is triggered in a manner similar to the ALARM [0] signal, with the difference that the temperature upper and lower limits for OT are generally larger than the upper and lower limits for ALARM [0] (corresponding to the temperature alarm), as shown in Figure 2-10.

Figure 2-10 Overview of Over-temperature Alarm Function

To eliminate OT glitches, after the signal indicating over-temperature in the module is pulled high (continuous high level), an internal counter operating in the clk\_mux clock domain begins counting, and OT only outputs a high level after counting to approximately 10ms. For control registers DB0 to DB2 (00h), please refer to the debounce counter description.

The default threshold upper limit for the over-temperature alarm is 125 C (creg\_2Ah=12'hCC2) and the lower limit is 50 C (creg\_2Bh=12'h A5B). Specific settings can be referred to in Table 2-11 Alarm Register List.

#### 2.6.2 Temperature Calibration Function

The ADC of each device will undergo temperature offset calibration during the production testing phase of the Logos2 FPGA. The temperature sensor calibration must be conducted strictly at 25 °C. The ADC first performs detection on the temperature sensor (two sampling settings of Avg=16 or 64 can be chosen, and the clock division is adjustable). The value tested under the current 25 °C condition is temp25, and the ADC calculates the Offset value: Offset\_temp=98Eh-temp25. This Offset\_temp value is written to the efuse via an internal configuration bus. Under normal operating conditions, when the ADC is performing temperature sensor monitoring, the ADC first detects the current temperature CODE, and then reads the Offset\_temp value of the temperature sensor from the efuse. The actual result of the ADC's monitored temperature is: CODE\_T=CODE – Offset\_temp, and this value is sent to the user and software, with the final conversion result being: Temperature(°C)=0.1219\*(CODE\_T)-273.15 (CODE\_T is in hexadecimal format)

Figure 2-11 Temperature Offset Calibration Diagram

Under normal operating conditions, temperature calibration is performed automatically after power-up, and production devices provide temperature values after calibration.

#### 2.7 Supply Voltage Monitoring

The ADC provides detection of on-chip voltages. The testable voltages are VCC, VCCA, VCC\_DRM, and VCC\_CRAM, with standard input values of  $1V\pm5\%$ ,  $1.8V\pm5\%$ ,  $1V\pm5\%$ , and  $1.25V\pm5\%$ , respectively; therefore, voltage division is required before testing.

| on-chip Voltage | Value Bef<br>Dividing | fore Voltage<br>(V) |       | Value Aft<br>(V) | Voltage<br>Dividing |       |       |

|-----------------|-----------------------|---------------------|-------|------------------|---------------------|-------|-------|

|                 | Min                   | Typical             | Max   | Min              | Typical             | Max   | Ratio |

| VCC             | 0.950                 | 1.000               | 1.050 | 0.316            | 0.333               | 0.350 | 1/3   |

| VCCA            | 1.710                 | 1.800               | 1.890 | 0.570            | 0.600               | 0.630 | 1/3   |

| VCC_DRM         | 0.950                 | 1.000               | 1.050 | 0.316            | 0.333               | 0.350 | 1/3   |

| VCC_CRAM        | 1.200                 | 1.250               | 1.300 | 0.400            | 0.417               | 0.430 | 1/3   |

Table 2-4 Typical Voltage Monitored by Voltage Sensor

Operate in Unipolar mode by default. The ADC divides the input supply voltage by 1/3. The conversion formula is:

Voltage=ADC Code/4096\*3V

Figure 2-12 Ideal Voltage Sensor Conversion Characteristics

#### 2.8 Register Description

Figure 2-13 shows the register interface for the ADC. There are two types of registers in the ADC: control registers and status registers. The value of the control register can be configured with initial values via parameters, and all registers can be accessed through APB or JTAG. The control register contains various control operations for the ADC and can be read and written; the status register stores the results of the ADC conversion calculations and is read-only.

After loading, the ADC will import user-configured parameters into the corresponding control registers, which can be accessed and modified via the APB interface or JTAG.

The default values of each register are based on the "UG040007 Logos2 Family Products GTP User Guide".

Figure 2-13 Register Interface

#### 2.8.1 Control Registers

The ADC has 24 control registers. For address mapping, please refer to Table 2-5. These register configurations are used for specific operations of the ADC and can be read and written. All ADC functions are controlled through these registers. The control registers primarily have 3 functions:

- 1. Set the working mode of the Logos2 ADC, such as clock frequency, ADC\_A/B status, and the alarm indicator switch.

- 2. Select the scanning channel, the corresponding bipolar or unipolar mode, and whether to enable averaging.

- 3. Set the maximum and minimum thresholds for voltage and on-chip temperature.

Table 2-5 Control Register Address Description

| Address                | Description    |

|------------------------|----------------|

| Configuration register |                |

| 00h                    | creg_00h[15:0] |

| 01h                    | creg_01h[15:0] |

| 02h                    | creg_02h[15:0] |

| Sequence Register      |                |

| Address                | Description             |

|------------------------|-------------------------|

| 03h                    | creg_03h[15:0]          |

| 04h                    | creg_04h[15:0]          |

| 05h                    | creg_05h[15:0]          |

| 06h                    | creg_06h[15:0]          |

| 07h                    | creg_07h[15:0]          |

| 08h                    | creg_08h[15:0]          |

| 10h                    | creg_0Ah[15:0]          |

| 12h                    | creg_0Ch[15:0]          |

| 14h                    | creg_0Eh[15:0]          |

| Alarm Control Register |                         |

| 20-2Bh                 | creg_20h~creg_2Bh[11:0] |

#### 2.8.1.1 Configuration Register

The configuration register (00h-02h) is used for specific configurations of some internal modules of the ADC. The value of the configuration register can be modified through APB or JTAG during the proper operation of the ADC. The specific definition of each bit is shown in Table 2-6.

|                | DI15 | DI14 | DI13      | DI12       | DI11       | DI10 | D19             | DI8             | DI7  | DI6             | DI5             | DI4         | DI3        | DI2       | DI1  | D10       |

|----------------|------|------|-----------|------------|------------|------|-----------------|-----------------|------|-----------------|-----------------|-------------|------------|-----------|------|-----------|

| creg_00h[15:0] | PD1  | PD0  | CLKS<br>W | SEQ        | RDAT<br>A  |      | DB2             | DB1             | DB0  |                 | ALM4            | ALM3        | ALM2       | ALM1      | ALMO | ОТ        |

|                |      |      |           |            |            |      |                 |                 |      |                 |                 |             |            |           |      |           |

| creg_01h[15:0] | CAL1 | CAL0 |           | AVG1       | AVG0       |      |                 |                 | DIV7 | DIV6            | DIV5            | DIV4        | DIV3       | DIV2      | DIV1 | DIV0      |

|                |      |      |           |            |            |      |                 |                 |      |                 |                 |             |            |           |      |           |

| creg_02h[15:0] | VCM1 | VCM0 | VREF      | SCAL<br>E1 | SCAL<br>E0 |      | INPUTR<br>ES_A1 | INPUT<br>RES_A0 |      | INPUT<br>RES_B1 | INPUT<br>RES_B0 | E_B_<br>VPN | Clk<br>gen | N_SE<br>Q | CE   | E_OS<br>C |

Figure 2-14 Configuration Register Bit Allocation

| Table 2-6 Configuration | on Register List |

|-------------------------|------------------|

|-------------------------|------------------|

| Bit             | Item               | Read/<br>Write | Description                                                                                                                                                                                             |  |

|-----------------|--------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| creg_00h        |                    |                |                                                                                                                                                                                                         |  |

| DI15 to<br>DI14 | PD1 to PD0         | R/W            | Power-down control bit, ADC_PD<br>[PD1: PD0]<br>00: Default, all modules powered up<br>01: Reserved<br>10: ADC B powered down<br>11: All modules powered down                                           |  |

| DI13            | CLKSW <sup>1</sup> | R/W            | Clock source switch control bit:<br>1: The system selects the DCLK of the APB interface for clock<br>division to generate ad_clk<br>0: The system selects clk_osc for clock division to generate ad_clk |  |

| DI12            | SEQ                | R/W            | Scanning mode selection bit:<br>1: Sequential scan mode<br>0: Power-up mode                                                                                                                             |  |

| DI11            | RDATA              | R/W            | Flag bit for bypassing error calibration process, meaning that data is stored directly in the status register. This function is not supported for                                                       |  |

| Bit             | Item                      | Read/<br>Write | Description                                                                                                                                                                                                                                                                                 |

|-----------------|---------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |                           |                | temperature and power voltage detection.<br>1: Valid, error calibration bypassed<br>0: Invalid                                                                                                                                                                                              |

| DI9 to<br>DI7   | DB2 to DB0                | R/W            | Set the debounce counter value for the over_temp signal. For details,<br>please refer to<br>Table 2-7 OT Signal Debounce Counter                                                                                                                                                            |

| DI5             | ALM4                      | R/W            | VCC_DRM voltage alarm output enable control bit:<br>1: Enable alarm<br>0: Disable alarm                                                                                                                                                                                                     |

| DI4             | ALM3                      | R/W            | VCC_CRAM voltage alarm output enable control bit:<br>1: Enable alarm<br>0: Disable alarm                                                                                                                                                                                                    |

| DI3             | ALM2                      | R/W            | VCCA voltage alarm output enable control bit:<br>1: Enable alarm<br>0: Disable alarm                                                                                                                                                                                                        |

| DI2             | ALM1                      | R/W            | VCC voltage alarm output enable control bit:<br>1: Enable alarm<br>0: Disable alarm                                                                                                                                                                                                         |

| DI1             | ALM0                      | R/W            | Temperature alarm output enable control bit:<br>1: Enable alarm<br>0: Disable alarm                                                                                                                                                                                                         |

| DI0             | ОТ                        | R/W            | Over-temperature enable flag bit (active-high)                                                                                                                                                                                                                                              |

| creg_01h        |                           |                |                                                                                                                                                                                                                                                                                             |

| DI15 to<br>DI14 | CAL1 to CAL0 <sup>2</sup> | R/W            | Calibration control configuration,<br>[CAL1:CAL0]<br>00: Disable offset and Gain calibration<br>01: Enable offset calibration<br>10: Enable gain calibration; Only valid in debug mode, invalid for<br>custom setting<br>11: Enable offset and Gain calibration                             |

| DI12 to<br>DI11 | AVG1 to AVG0 <sup>2</sup> | R/W            | ADC average control bit<br>[AVG1:AVG0]<br>00: Non-averaging<br>01: Averaging over 16 samples<br>10: Averaging over 64 samples<br>11: Averaging over 256 samples<br>Note that in 2-channel mode, the non-averaging setting<br>([AVG1:AVG0]=2'b00) is not supported when using division by 2. |

| DI9 to<br>DI8   | CD1 to CD0                | R/W            | Control the clock divider during the calibration sampling process<br>[CD1:CD0]<br>00: Calibration clock division factor is 16<br>01: Calibration clock division factor is 16<br>10: Calibration clock division factor is 32<br>11: Calibration clock division factor is 64                  |

| DI7 to<br>DI0   | DIVA7 to DIVA0            | R/W            | Clock division signal for ADC. For details, please refer to Table 2-8<br>Clock Division Control                                                                                                                                                                                             |

| creg_02h        |                           |                |                                                                                                                                                                                                                                                                                             |

| DI15 to<br>DI14 | VCM1 to VCM0              | R/W            | Reserved, maintain the fixed value 00.                                                                                                                                                                                                                                                      |

| DI13            | VREF <sup>2</sup>         | R/W            | Select reference source for ADC<br>0: Internal reference source<br>1: External reference source                                                                                                                                                                                             |

| DI12 to<br>DI11 | SCALE[1] to<br>SCALE[0]   | R/W            | Reserved, maintain the fixed value 00.                                                                                                                                                                                                                                                      |

| Bit           | Item                              | Read/<br>Write | Description                                                                                                                                                                                                                                  |  |

|---------------|-----------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DI9 to<br>DI8 | INPUT_RESA[1] to<br>INPUT_RESA[0] | R/W            | Reserved, maintain the fixed value 00.                                                                                                                                                                                                       |  |

| DI6 to<br>DI5 | INPUT_RESB[1] to<br>INPUT_RESB[0] | R/W            | Reserved, maintain the fixed value 00.                                                                                                                                                                                                       |  |

| DI4           | E_B_VPN                           | R/W            | <ul> <li>ADC_B enable signal for scanning dedicated channels:</li> <li>0: creg_03h/05h/07h[14] controls ADC_A's scanning of dedicated channels;</li> <li>1: creg_03h/05h/07h[14] controls ADC_B's scanning of dedicated channels.</li> </ul> |  |

| DI3           | CLKGEN                            | R/W            | Clock generation enable signal                                                                                                                                                                                                               |  |

| DI2           | N_SEQ                             | R/W            | Control bit used to generate the scan signal in event-driven sampling state.                                                                                                                                                                 |  |

| DI1           | CE                                | R/W            | Continuous sampling mode and event-driven sampling mode<br>selection bit<br>0: Continuous sampling<br>1: Event-driven sampling                                                                                                               |  |

| DI0           | E_OSC                             | R/W            | <ul> <li>Built-in clk_osc switch enable signal</li> <li>0: Control the clk_osc switch according to the system's clkswitch and</li> <li>PD0 control bit;</li> <li>1: clk_osc is always on, unaffected by other signals.</li> </ul>            |  |

Notes:

1. When the user selects DCLK, the ADC configuration loading is triggered upon receiving the LOADSC\_N signal at a low level. For detailed timing of the LOADSC\_N signal, please refer to Figure 2–3; when the user selects clk\_osc, the ADC configuration can be automatically loaded.

2. To meet the detection accuracy requirements for on-chip temperature and on-chip supply voltage with  $-40^{\circ}C \le Tj \le 100^{\circ}C$ , it is necessary to enable offset and gain calibration, average 64 samples or 256 samples, and simultaneously use an external high-precision VREF voltage. The external VREF should be maintained within the range of  $1.255V\pm0.2\%$ .

| CLKSW<br>Configuration | DB2 | DB1 | DB0 | Corresponding Source Clock<br>Cycle Corresponding Counter Si |            |

|------------------------|-----|-----|-----|--------------------------------------------------------------|------------|

| 1, DCLK                | 0   | 0   | 0   | 1000ns>DCLK cycle≥850ns                                      | 20'h 03000 |

| 1, DCLK                | 0   | 0   | 1   | 850ns>DCLK cycle≥650ns                                       | 20'h 04000 |

| 1, DCLK                | 0   | 1   | 0   | 650ns>DCLK cycle≥500ns                                       | 20'h 05000 |

| 1, DCLK                | 0   | 1   | 1   | 500ns>DCLK cycle≥300ns                                       | 20'h 09000 |

| 1, DCLK                | 1   | 0   | 0   | 300ns>DCLK cycle≥150ns 20'h 20000                            |            |

| 1, DCLK                | 1   | 0   | 1   | 150ns>DCLK cycle≥50ns                                        | 20'h 40000 |

| 1, DCLK                | 1   | 1   | 0   | 50ns>DCLK cycle≥10ns                                         | 20'h F5000 |

| 1, DCLK                | 1   | 1   | 1   | N/A                                                          | N/A        |

| 0, clk_osc             | Х   | Х   | Х   | clk_osc cycle 20ns 20'h 80000                                |            |

Note: To eliminate OT signal glitches, when the temperature exceeds the threshold of creg\_2Ah, the ADC internal counter starts counting. The counter size is set through DB2~DB0 based on the source clock frequency. When the count value reaches its upper limit, the OT signal outputs high level.

| DIVA7 DIVA6 DIVA5 DIVA4 DIVA3 DIVA2 DIVA1 DIVA0 Division Ratio |

|----------------------------------------------------------------|

|----------------------------------------------------------------|

| DIVA7 | DIVA6 | DIVA5 | DIVA4 | DIVA3 | DIVA2 | DIVA1 | DIVA0 | <b>Division Ratio</b> |

|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 2                     |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 2                     |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 4                     |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 4                     |

| 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 6                     |

| 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1     | 6                     |

|       |       |       |       |       |       |       |       |                       |

| 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     | 254                   |

| 1     | 1     | 1     | 1     | 1     | 1     | 0     | 1     | 254                   |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 256                   |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 256                   |

#### 2.8.1.2 Sequence Register

Like the configuration register, the value of the sequence register can be modified through APB or JTAG at any time during the proper operation of the ADC. The definition of each bit is shown in Table 2-9.

|                | DI 15       | DI14        | DI 13       | DI 12       | DI 11       | DI 10       | D19        | DI8        | DI7        | DI6        | DI5        | DI4        | DI3        | DI2        | DI1        | DI0        |

|----------------|-------------|-------------|-------------|-------------|-------------|-------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| creg_03h[15:0] | AC 15       | AC14        | AC13        | AC 12       | AC 11       | AC10        | AC9        | AC8        | AC7        | AC6        | AC5        | AC4        | AC3        | AC2        | AC1        | AC0        |

|                |             |             |             |             |             |             |            |            |            |            |            |            |            |            |            |            |

| creg_04h[15:0] | AXC1<br>5   | AXC 1<br>4  | AXC 1<br>3  | AXC1<br>2   | AXC1<br>1   | AXC 1<br>0  | AXC 9      | AXC 8      | AXC 7      | AXC 6      | AXC 5      | AXC 4      | AXC 3      | AXC 2      | AXC 1      | AXC 0      |

|                |             |             |             |             |             |             |            |            |            |            |            |            |            |            |            |            |

| creg_05h[15:0] | ABU 1<br>5  | ABU 1<br>4  | ABU 1<br>3  | ABU 1<br>2  | ABU1<br>1   | ABU 1<br>0  | ABU 9      | ABU 8      | ABU 7      | ABU 6      | ABU 5      | ABU 4      | ABU 3      | ABU 2      | ABU 1      | ABU 0      |

|                |             |             |             |             |             |             |            |            |            |            |            |            |            |            |            |            |

| creg_06h[15:0] | AXBU<br>15  | AXBU<br>14  | AXBU<br>13  | AXBU<br>12  | AXBU<br>11  | AXBU<br>10  | AXBU<br>9  | AXBU<br>8  | AXBU<br>7  | AXBU<br>6  | AXBU<br>5  | AXBU<br>4  | AXBU<br>3  | AXBU<br>2  | AXBU<br>1  | AXBU<br>0  |

|                |             |             |             |             |             |             |            |            |            |            |            |            |            |            |            |            |

| creg_07h[15:0] | ACAV<br>15  | ACAV<br>14  | ACAV<br>13  | ACAV<br>12  | ACAV<br>11  | ACAV<br>10  | ACAV<br>9  | ACAV<br>8  | ACAV<br>7  | ACAV<br>6  | ACAV<br>5  | ACAV<br>4  | ACAV<br>3  | ACAV<br>2  | ACAV<br>1  | ACAV<br>0  |

|                |             |             |             |             |             |             |            |            |            |            |            |            |            |            |            |            |

| creg_08h[15:0] | AXCAV<br>15 | AXCAV<br>14 | AXCAV<br>13 | AXCAV<br>12 | AXCAV<br>11 | AXCAV<br>10 | AXCAV<br>9 | AXCAV<br>8 | AXCAV<br>7 | AXCAV<br>6 | AXCAV<br>5 | AXCAV<br>4 | AXCAV<br>3 | AXCAV<br>2 | AXCAV<br>1 | AXCAV<br>0 |

|                |             |             |             |             |             |             |            |            |            |            |            |            |            |            |            |            |

| creg_0Ah[15:0] | BXC<br>15   | BXC<br>14   | BXC<br>13   | BXC<br>12   | BXC<br>11   | BXC<br>10   | BXC 9      | BXC 8      | BXC7       | BXC 6      | BXC 5      | BXC 4      | BXC 3      | BXC 2      | BXC 1      | BXC 0      |

|                |             |             |             |             |             |             |            |            |            |            |            |            |            |            |            |            |

| creg_0Ch[15:0] | BXBU<br>15  | BXBU<br>14  | BXBU<br>13  | BXBU<br>12  | BXBU<br>11  | BXBU<br>10  | BXBU<br>9  | BXBU<br>8  | BXBU<br>7  | BXBU<br>6  | BXBU<br>5  | BXBU<br>4  | BXBU<br>3  | BXBU<br>2  | BXBU<br>1  | BXBU<br>0  |

|                |             |             |             |             |             |             |            |            |            |            |            |            |            |            |            |            |

| creg_0Eh[15:0] | BXCAV<br>15 | BXCAV<br>14 | BXCAV<br>13 | BXCAV<br>12 | BXCAV<br>11 | BXCAV<br>10 | BXCAV<br>9 | BXCAV<br>8 | BXCAV<br>7 | BXCAV<br>6 | BXCAV<br>5 | BXCAV<br>4 | BXCAV<br>3 | BXCAV<br>2 | BXCAV<br>1 | BXCAV<br>0 |

| Item | Read/<br>Write | Description                                                      |

|------|----------------|------------------------------------------------------------------|

|      |                |                                                                  |

|      |                | ADC_A internal voltage, temperature and dedicated channel enable |

For the correspondence between each bit and channel, please refer

1: Valid;

0: Invalid;

R/W

| Table 2-9 | Sequence | Register List |

|-----------|----------|---------------|

|-----------|----------|---------------|

AC0~AC15

Bit

creg\_03h

DI0~DI15

| Bit      | Item               | Read/<br>Write | Description                                                                                                                                                                                                                                                            |

|----------|--------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                    |                | to Table 2-10 Sequence Register Dedicated Channel Bit Mapping<br>Relationship (ADC_B does not scan internal voltage, temperature)                                                                                                                                      |

| creg_04h |                    |                |                                                                                                                                                                                                                                                                        |

| DI0~DI15 | AXC0~AXC15         | R/W            | ADC_A external multiplex channel enable<br>1: Valid;<br>0: Invalid;<br>DI0~15 correspond to multiplex channels 0~15                                                                                                                                                    |

| creg_05h |                    |                |                                                                                                                                                                                                                                                                        |

| DI0~DI15 | ABU0~ABU15         | R/W            | ADC_A internal voltage, temperature and dedicated channel scan<br>mode selection<br>1: Bipolar;<br>0: Unipolar;<br>For the correspondence between each bit and channel please refer<br>to Table 2-10 Sequence Register Dedicated Channel Bit Mapping<br>Relationship   |

| creg_06h |                    |                |                                                                                                                                                                                                                                                                        |

| DI0~DI15 | AXBU0~AXBU15       | R/W            | ADC_A external multiplex channel scan mode selection<br>1: Bipolar;<br>0: Unipolar;<br>DI0~15 correspond to multiplex channels 0~15                                                                                                                                    |

| creg_07h |                    |                |                                                                                                                                                                                                                                                                        |

| DI0~DI15 | ACAV0~ACAV15       | R/W            | ADC_A internal voltage, temperature and dedicated channel<br>averaging mode selection<br>1: Valid;<br>0: Invalid;<br>For the correspondence between each bit and channel please refer<br>to Table 2-10 Sequence Register Dedicated Channel Bit Mapping<br>Relationship |

| creg_08h |                    |                |                                                                                                                                                                                                                                                                        |

| DI0~DI15 | AXCAV0~<br>AXCAV15 | R/W            | ADC_A external multiplex channel averaging mode selection<br>1: Valid;<br>0: Invalid;<br>DI0~15 correspond to multiplex channels 0~15                                                                                                                                  |

| creg_0Ah |                    |                |                                                                                                                                                                                                                                                                        |

| DI0~DI15 | BXC0~BXC15         | R/W            | ADC_B external multiplex channel enable<br>1: Valid;<br>0: Invalid;<br>DI0~15 correspond to multiplex channels 0~15                                                                                                                                                    |

| creg_0Ch |                    |                |                                                                                                                                                                                                                                                                        |

| DI0~DI15 | BXBU0~BXBU15       | R/W            | ADC_B external multiplex channel scan mode selection<br>1: Bipolar;<br>0: Unipolar;<br>DI0~15 correspond to multiplex channels 0~15                                                                                                                                    |

| creg_0Eh |                    |                |                                                                                                                                                                                                                                                                        |

| DI0~DI15 | BXCAV0~<br>BXCAV15 | R/W            | ADC_B external multiplex channel averaging mode selection<br>1: Valid;<br>0: Invalid;<br>DI0~15 correspond to multiplex channels 0~15                                                                                                                                  |

Notes:

1. The channel modes and averaging control bits only take effect when the corresponding channel selection enables for  $creg_03/04/0Ah$ .

2. PG2L100H, currently does not support switching Unipolar/Bipolar mode during multi-channel switching; ADC\_A or ADC\_B channels only support being fully configured as Unipolar or Bipolar mode.

| Bit  | Corresponding Channel                  | Scan Mode        |

|------|----------------------------------------|------------------|

| 0~1  | For internal calibration use, not open | N/A              |

| 2    | Temperature                            | Unipolar         |

| 3    | VCC                                    | Unipolar         |

| 4    | VCCA                                   | Unipolar         |

| 5    | VCC_CRAM                               | Unipolar         |

| 6    | VCC_DRM                                | Unipolar         |

| 7~8  | For internal calibration use, not open | N/A              |

| 9~13 | Not used                               | N/A              |

| 14   | Dedicated channel                      | Unipolar/Bipolar |

| 15   | Not used                               | N/A              |

| Table 2-10 Sequence Register Dedicated Channel B | it Mapping Relationship |

|--------------------------------------------------|-------------------------|

|--------------------------------------------------|-------------------------|

#### 2.8.1.3 Alarm Registers

|              | DI11                      | DI10 | DI9 | DI8 | DI7 | DI6 | DI5 | DI4 | DI3 | DI2 | DI1 | DI0 |

|--------------|---------------------------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| creg_20h~2Bh | Alarm threshold registers |      |     |     |     |     |     |     |     |     |     |     |

Figure 2-16 Alarm Register Bit Allocation

| Alarm<br>Control | Read/Write         | Description                                                          | Corresponding Control<br>Bit |  |  |

|------------------|--------------------|----------------------------------------------------------------------|------------------------------|--|--|

| creg_20h         | R/W                | Temperature record alarm threshold upper limit setting               | area 00h ALMO anchia         |  |  |

| creg_21h         | R/W                | Temperature record alarm threshold lower limit setting               | creg_00h ALM0 enable         |  |  |

| creg_22h         | R/W                | VCC record alarm threshold upper limit setting                       | and OOL ALM1 and L           |  |  |

| creg_23h         | R/W                | VCC record alarm threshold lower limit setting                       | creg_00h ALM1 enable         |  |  |

| creg_24h         | R/W                | VCCA record alarm threshold upper limit setting                      | and 00h ALMO angle           |  |  |

| creg_25h         | R/W                | VCCA record alarm threshold lower limit setting                      | creg_00h ALM2 enable         |  |  |

| creg_26h         | R/W                | VCC_CRAM record alarm threshold upper limit setting                  |                              |  |  |

| creg_27h         | R/W                | VCC_CRAM record alarm threshold lower limit setting                  | creg_00h ALM3 enable         |  |  |

| creg_28h         | R/W                | VCC_DRM record alarm threshold upper limit setting                   |                              |  |  |

| creg_29h R/W     |                    | VCC_DRM record alarm threshold lower limit setting                   | creg_00h ALM4 enable         |  |  |

| creg_2Ah         | R/W                | Over-temperature alarm reporting upper limit setting                 |                              |  |  |

| creg_2Bh R/W     |                    | Over-temperature alarm clearing lower limit setting                  | creg_00h OT enable           |  |  |

| Note: The corres | sponding threshold | settings take effect only after the corresponding control bits in cr | eg_00h are enabled.          |  |  |

#### Table 2-11 Alarm Register List

#### 2.8.2 Status Registers

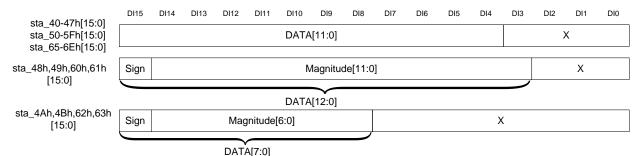

Status registers (40h to 6Eh) store the conversion results for each channel as well as the offset and gain error values for calibration. All status registers can only be read by the user and cannot be written to.

The following is the definition of each address bit in the status register:

| Address | Defaults  | Read/Write | Description                                                               |

|---------|-----------|------------|---------------------------------------------------------------------------|

| 40h     | 16'h 0000 | RO         | Converted temperature                                                     |

| 41h     | 16'h 0000 | RO         | Converted VCC                                                             |

| 42h     | 16'h 0000 | RO         | Converted VCCA                                                            |

| 43h     | 16'h 0000 | RO         | Converted VCC_CRAM                                                        |

| 44h     | 16'h 0000 | RO         | Converted VCC_DRM                                                         |

| 45h     | 16'h 0000 | RO         | Converted dedicated channel VAADC_P/VAADC_N                               |

| 46h     | 16'h 0000 | RO         | Converted calibration code0                                               |

| 47h     | 16'h 0000 | RO         | Converted calibration code1                                               |

| 48h     | 16'h 0000 | RO         | Converted ADC_A Offset (Unipolar)                                         |

| 49h     | 16'h 0000 | RO         | Converted ADC_A Offset (Bipolar)                                          |

| 4Ah     | 16'h 0000 | RO         | Converted ADC_A Gain (Unipolar)                                           |

| 4Bh     | 16'h 0000 | RO         | Converted ADC_A Gain (Bipolar)                                            |

| 4Ch     | 16'h 0000 | RO         | Converted ADC_A supply sensor Offset (Unipolar)                           |

| 50-5Fh  | 16'h 0000 | RO         | Converted VAA[0:15]P/VAA[0:15] NMultiplexed channel 0-15                  |

| 60h     | 16'h 0000 | RO         | Converted ADC_B Offset (Unipolar)                                         |

| 61h     | 16'h 0000 | RO         | Converted ADC_B Offset (Bipolar)                                          |

| 62h     | 16'h 0000 | RO         | Converted ADC_B Gain (Unipolar)                                           |

| 63h     | 16'h 0000 | RO         | Converted ADC_B Gain (Bipolar)                                            |

| 65h     | 16'h 0000 | RO         | Temperature after the maximum conversion since the last power-up or reset |

| 66h     | 16'h 0000 | RO         | VCC after the maximum conversion since the last power-up or reset         |

| 67h     | 16'h 0000 | RO         | VCCA after the maximum conversion since the last power-up or reset        |

| 68h     | 16'h 0000 | RO         | VCC_CRAM after the maximum conversion since the last power-up or reset    |

| 69h     | 16'h 0000 | RO         | VCC_DRM after the maximum conversion since the last power-up or reset     |

| 6Ah     | 16'h FFF0 | RO         | Temperature after the minimum conversion since the last power-up or reset |

| 6Bh     | 16'h FFF0 | RO         | VCC after the minimum conversion since the last power-up or reset         |

| 6Ch     | 16'h FFF0 | RO         | VCCA after the minimum conversion since the last power-up or reset        |

| 6Dh     | 16'h FFF0 | RO         | VCC_CRAM after the minimum conversion since the last power-up or reset    |

| 6Eh     | 16'h FFF0 | RO         | VCC_DRM after the minimum conversion since the last power-up or reset     |

| Table 2-12 Status Register Lis | Table | 2-12 | Status | Register | List |

|--------------------------------|-------|------|--------|----------|------|

|--------------------------------|-------|------|--------|----------|------|

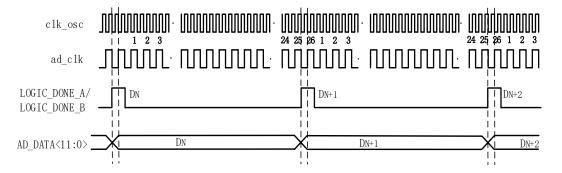

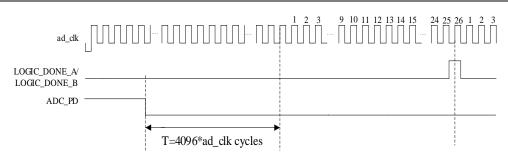

Figure 2-17 Status Register Data Structure Diagram

After each reset and power-up, the register storing the minimum value will be reset to FFFFh, and the register storing the maximum value will be reset to 0000h. Each signal detected must be compared with the set threshold values. If the detected value exceeds the upper limit, it will be stored in the corresponding maximum value register within the status registers. Similarly, if the detected value is below the lower limit, it will be stored in the corresponding minimum value register within the status registers.

For the value of the offset register, the upper 13 bits represent the significant digits, with the highest bit being the sign bit. If the ADC offset is -10 LSBs (10\*-0.244mV=-2.44mV), the value stored in the offset register is -10 LSBs, i.e., FF6h, and the value recorded in the status register is 1111\_1111\_1011\_0xxxb.

For the value of the gain register, the upper 8 bits represent the significant digits, with the highest bit being the sign bit. If the ADC gain is +1%, the gain register stores the value +1%, with the LSB being 0.1%. Thus 1% = 10\*0.1%, and the register value is  $0000\_1010\_xxxx\_xxxxb$ . The maximum value recorded by the register is  $\pm 0.1\%*63=\pm 6.3\%$ .

#### 2.9 ADC Operating Modes

Logos2 ADC supports two working modes:

- > Power-up mode, which detects on-chip voltages and temperature;

- Scan sequence mode, which scans selected channels based on the control register settings.

After power-up, glogen=0 (glogen is the system build indicator, glogen=0 means no build has been performed), the system automatically performs calibration and enters Power-Up Mode. When glogen=1 (after the system build), the system performs the corresponding mode or channel scan according to the settings in the control register.

In addition to power-up reset and active reset, a soft reset signal is generated when creg\_00h and creg\_01h are rewritten. When this reset occurs, the Logos2 ADC restarts to execute the newly

written modes. The values in the status register are not affected by this reset.