Compa

Compa Family CPLDs use mature processes and independent IP architecture to meet the requirements of low-power, low-cost and low-space design. It is suitable for system configuration, interface expansion and bridging, board-level power management, power-up timing management, sensor fusion and other application requirements, and can be widely used in fields such as Communications, Consumer, and Industrial Control applications.

Product Features

Product Selection Guide

| Device Number1 | PGC1K | PGC2K | PGC4K | PGC7K | PGC10K | ||

| Logic resources | logic Cell | 1276 | 2428 | 4761 | 7104 | 9907 | |

| LUTs | 1064 | 2024 | 3968 | 5902 | 8256 | ||

| Flip-Flop | 1596 | 3036 | 5952 | 8880 | 12384 | ||

| RAM resources | Distributed RAM(Kbit) | 11 | 16 | 39 | 56 | 78 | |

| Embedded 9K block RAM | 7 | 8 | 11 | 26 | 45 | ||

| Memory blocks(Kbit) | 63 | 72 | 99 | 234 | 405 | ||

| Flash resources | Maximum embedded Flash capacity available to users(Kbits)2 | 310 | 80 | 1520 | 2070 | 3016 | |

| Clock resources | Phase Locked Loop (PLL)/Global Clock | 1/16 | 1/16 | 2/16 | 2/16 | 2/16 | |

| IO resources | IO Banks | 4 | 6 | 6 | 6 | 6 | |

| Maximum user I/Os | 207 | 207 | 280 | 336 | 384 | ||

| Maximum differential pairs | 14 | 14 | 18 | 21 | 24 | ||

| Hard core resources | I2C hard core | 2 | 2 | 2 | 2 | 2 | |

| SPI hard core | 1 | 1 | 1 | 1 | 1 | ||

| Timer/counter hard core | 1 | 1 | 1 | 1 | 1 | ||

| On-chip oscillator | 1 | 1 | 1 | 1 | 1 | ||

| Power-up initiation time (ms) | 2.264 | 2.264 | 3 | 4.67 | 7.3 | ||

| Package | Dimensions(mm) | Ball Pitch(mm) | User IO / Differential pairs | ||||

| UWG363 | 2.5 x 2.5 | 0.4 | 29/34 | ||||

| UWG49 | 3.2 x 3.2 | 0.4 | 39/5 | ||||

| UWG81 | 3.8 x 3.8 | 0.4 | 64/10 | ||||

| QFN32 | 5 x 5 | 0.5 | 21/0 | ||||

| QFN48 | 7 x 7 | 0.5 | 38/0 | ||||

| SSBG2563 | 9 x 9 | 0.5 | 207/14 | ||||

| LPG100 | 14 x 14 | 0.5 | 80/4 | 80/4 | |||

| LPG144 | 20 x 20 | 0.5 | 112/9 | 112/9 | 115/9 | 115/9 | |

| MBG256 | 14 x 14 | 0.8 | 207/14 | 207/14 | 207/18 | 207/20 | |

| FBG256 | 17 x 17 | 1 | 207/14 | 207/14 | 207/18 | ||

| SBG132 | 8 x 8 | 0.5 | 104/8 | ||||

| MBG324 | 15 x 15 | 0.8 | 280/18 | ||||

| MBG400 | 17 x 17 | 0.8 | 336/21 | 336/22 | |||

| MBG484 | 19 x 19 | 0.8 | 384/24 | ||||

| Notes: 1、PGC1K/PGC2K support version G (General) and version L (Low-Power) devices; PGC4K supports version L and version D (Dual Boot function) devices; PGC7K/PGC10K support version D devices. 2、Remaining maximum Flash capacity when not using the Dual Boot function. 3、UWG and SSBG packages are only available in the 1.2 V low-voltage version. |

|||||||

Technical Documentation

-

PK03028_PGC4KLS_SBG81_V1.0

PK03028_PGC4KLS_SBG81_V1.0 2024.03.22

2024.03.22

-

PK03026_PGC10KD_MBG484_V1.0

PK03026_PGC10KD_MBG484_V1.0 2024.03.22

2024.03.22

-

PK03023_PGC4KL_UWG81_V1.2

PK03023_PGC4KL_UWG81_V1.2 2024.03.22

2024.03.22

-

PK03015_PGC4KD_FBG256_V1.2

PK03015_PGC4KD_FBG256_V1.2 2024.03.22

2024.03.22

-

PK03011_PGC7KD_MBG400_V1.2

PK03011_PGC7KD_MBG400_V1.2 2024.03.22

2024.03.22

-

PK03009_PGC1KL_UWG36_V1.3

PK03009_PGC1KL_UWG36_V1.3 2024.03.22

2024.03.22

-

PK03005_PGC1KG_FBG256_V1.7

PK03005_PGC1KG_FBG256_V1.7 2024.03.22

2024.03.22

-

PK03003_PGC2KL_UWG49_V1.8

PK03003_PGC2KL_UWG49_V1.8 2024.03.22

2024.03.22

-

UG030009_Compa Family PCB Design User Guide_V1.1

UG030009_Compa Family PCB Design User Guide_V1.1 2024.03.22

2024.03.22

-

UG030008_Compa Family GTP User Guide_V1.2

UG030008_Compa Family GTP User Guide_V1.2 2024.03.22

2024.03.22

-

UG030007_Compa Family CPLDs Embedded Hard Core User Guide_V1.3

UG030007_Compa Family CPLDs Embedded Hard Core User Guide_V1.3 2024.03.22

2024.03.22

-

UG030006_Compa Family CPLDs Embedded Flash (EFlash) User Guide_V1.2

UG030006_Compa Family CPLDs Embedded Flash (EFlash) User Guide_V1.2 2024.03.22

2024.03.22

-

UG030005_Compa Family CPLDs Input Output Interface (IO) User Guide_V1.3

UG030005_Compa Family CPLDs Input Output Interface (IO) User Guide_V1.3 2024.03.22

2024.03.22

-

UG030004_Compa Family CPLDs Configuration User Guide_V1.7

UG030004_Compa Family CPLDs Configuration User Guide_V1.7 2024.03.22

2024.03.22

-

UG030003_Compa Family CPLDs Clock Resources User Guide_V1.4

UG030003_Compa Family CPLDs Clock Resources User Guide_V1.4 2024.03.22

2024.03.22

-

UG030002 Compa Family CPLDs Dedicated RAM Module (DRM) User Guide_1.2

UG030002 Compa Family CPLDs Dedicated RAM Module (DRM) User Guide_1.2 2024.03.22

2024.03.22

-

UG030001 Compa Family CPLDs Configurable Logic Module (CLM) User Guide_1.3

UG030001 Compa Family CPLDs Configurable Logic Module (CLM) User Guide_1.3 2024.03.22

2024.03.22

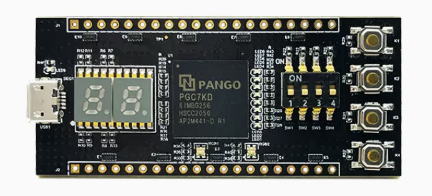

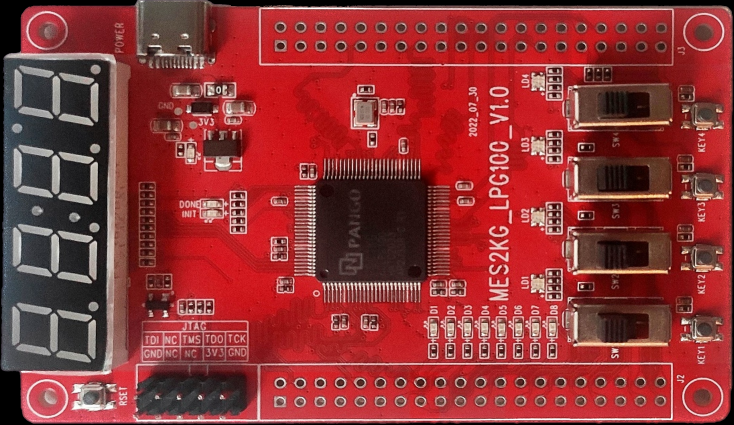

Development Boards and Kits

- Products Titan Family Logos Family Compa Family Pango Design Suite

- Solutions Communication Industrial Image&Video Consumer Auto Data center Other

- Resource Software and license IP Partners

- About us Company profile Contact us Announcement

-

Contact us

86-755-66886188

marketing@pangomicro.com

No. 15, Gaoxin South Road,

High-Tech Industrial Park,

Nanshan District, Shenzhen

Official public account

Official public account

©2023 All Rights Reserved Shenzhen Pango Microsystems Co., Ltd. Guangdong ICP Filing No. 14029535